西藏半導體PAT解決方案

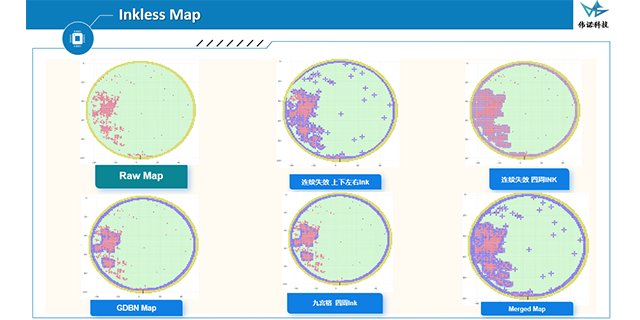

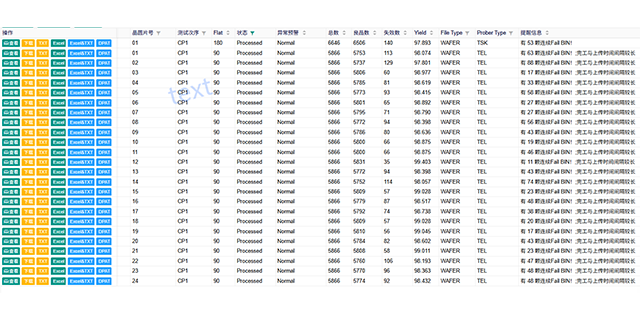

面對國產半導體制造對自主可控軟件的迫切需求,良率管理系統成為打通數據孤島、實現質量閉環的關鍵工具。系統自動采集ETS88、93k、J750、Chroma等主流Tester平臺輸出的stdf、csv、xls、log、spd、jdf、zip、txt等多種格式測試數據,通過內置算法識別重復項、缺失值并過濾異常記錄,確保后續分析基于高可信度數據源。在標準化數據庫支撐下,企業可從時間維度追蹤良率趨勢,或聚焦晶圓特定區域對比缺陷分布,快速定位工藝波動點。結合WAT、CP與FT參數的聯動分析,進一步揭示影響良率的深層原因。SYL與SBL的自動計算與卡控機制,強化了過程質量防線。靈活的報表工具支持按模板生成日報、周報、月報,并導出為PPT、Excel或PDF格式,提升跨部門協同效率。上海偉諾信息科技有限公司自2019年成立以來,專注打造適配本土需求的YMS系統,助力構建中國半導體軟件生態。Mapping Over Ink處理通過空間分析有效識別外觀損傷引起的隱性失效,提升可靠性。西藏半導體PAT解決方案

面對市場上良率管理系統供應商良莠不齊的局面,技術自主性與行業適配能力成為選型主要標準。真正有效的系統需同時支持多品牌Tester設備、處理異構數據格式,并具備深度分析與可視化能力。YMS系統已集成ETS364、SineTest、ASL1000、MS7000、Juno、AMIDA、CTA8280、T861等設備的數據接口,覆蓋stdf、csv、log等十余種格式,實現一次接入、全域兼容。其分析引擎不僅支持時間趨勢與晶圓區域對比,還能關聯WAT、CP、FT參數變化,精確定位根因。更重要的是,系統背后有完整的實施與服務體系支撐,確保從部署到優化的每個環節穩定可控。這種軟硬協同的能力,使YMS在國產替代進程中脫穎而出。上海偉諾信息科技有限公司依托多年項目經驗,持續驗證其作為可靠供應商的技術實力與服務承諾。陜西晶圓GDBC系統定制工藝工程師基于GDBC聚類結果優化制程參數,提升制造良率水平。

ZPAT 是一種基于統計學的芯片篩選技術,通過在晶圓測試階段識別并剔除具有潛在缺陷的芯片,從而提升產品的可靠性。在實際的應用過程中需要通過疊加多片Wafer找出在同一坐標下失效的Die的比例,通過特定的算法從而評估其他未失效的Die存在的潛在失效的概率。也是提升芯片質量零缺陷的一種手段。

為助力客戶應對日益嚴苛的“零缺陷”質量挑戰,上海偉諾信息科技有限公司將其先進的ZPAT技術深度整合于Mapping Over Ink 解決方案中。這一創新集成賦予用戶高度的靈活性與強大的分析能力,使其能夠通過一套高度可配置的流程,精確、高效地剔除晶圓上那些性能參數超出統計控制界限的異常芯片,從而構筑起一道基于動態統計過程控制的智能質量防線。

在半導體工廠高頻率、多設備并行的測試環境中,人工處理異構數據極易延誤問題響應。YMS系統通過自動化流程,實時匯聚來自STS8200、TR6850、ASL1000、MS7000等設備的多格式原始數據,完成統一解析與清洗,消除因格式差異導致的信息斷層。結構化的數據庫使良率數據可追溯、可比對,支持從批次到晶圓級別的精細監控。當某一批次良率驟降時,系統可迅速調取對應區域的缺陷熱力圖,并關聯WAT、CP、FT參數變化,輔助工程師在數小時內鎖定根本原因。SYL/SBL卡控功能則在指標超限時自動預警,防止不良品流入下一環節。周期性報表一鍵生成并支持多格式導出,滿足從產線到高管的差異化信息需求。上海偉諾信息科技有限公司憑借對封測與制造場景的深入理解,持續優化YMS的數據驅動能力。Mapping Over Ink處理通過失效分布圖譜直觀暴露制造流程異常,指導工藝改進方向。

一套高效的良率管理系統開發方案,必須根植于真實生產場景的數據流與決策鏈。YMS方案覆蓋從ETS88、93k、J750等Tester平臺自動采集stdf、csv、log等多格式數據,到解析、清洗、整合的完整鏈路,確保數據源頭的完整性與一致性。在此基礎上,系統構建標準化數據庫,實現對良率信息的統一分類與高效調用。分析層面,方案強調時間序列下的良率波動追蹤與晶圓空間維度的缺陷聚類,結合WAT、CP、FT參數變化,形成從現象到根因的完整證據鏈。SYL與SBL的自動卡控機制嵌入關鍵控制點,實現預防性質量管理。同時,報表引擎支持按需生成周期報告,并導出為PPT、Excel或PDF,適配不同管理層的信息消費習慣。上海偉諾信息科技有限公司依托多年行業積累,將YMS方案打造為兼具實用性與擴展性的國產選擇。Mapping Over Ink處理助力國產軟件生態建設,推動技術自主可控。西藏半導體PAT解決方案

Mapping Over Ink處理的異常Die剔除決策具備完整數據留痕,確保處理過程透明可審計。西藏半導體PAT解決方案

在半導體制造中,由于Fab制程的物理與化學特性,晶圓邊緣的芯片(Edge Die)其失效率明顯高于中心區域。這一現象主要源于幾個關鍵因素:首先,在光刻、刻蝕、薄膜沉積等工藝中,晶圓邊緣的反應氣體流場、溫度場及壓力場分布不均,導致工藝一致性變差;其次,邊緣區域更容易出現厚度不均、殘留應力集中等問題;此外,光刻膠在邊緣的涂覆均勻性也通常較差。這些因素共同導致邊緣芯片的電氣參數漂移、性能不穩定乃至早期失效風險急劇升高。因此,在晶圓測試(CP)的制造流程中,對電性測試圖譜(Wafer Mapping)執行“去邊”操作,便成為一項提升產品整體良率與可靠性的關鍵步驟。

上海偉諾信息科技有限公司Mapping Over Ink功能中的Margin Map功能提供多種算法與自定義圈數,滿足客戶快速高效低剔除邊緣芯片,可以從根本上避免后續對這些潛在不良品進行不必要的封裝和測試,從而直接節約成本,并確保出廠產品的質量與可靠性要求。西藏半導體PAT解決方案

上海偉諾信息科技有限公司在同行業領域中,一直處在一個不斷銳意進取,不斷制造創新的市場高度,多年以來致力于發展富有創新價值理念的產品標準,在上海市等地區的數碼、電腦中始終保持良好的商業口碑,成績讓我們喜悅,但不會讓我們止步,殘酷的市場磨煉了我們堅強不屈的意志,和諧溫馨的工作環境,富有營養的公司土壤滋養著我們不斷開拓創新,勇于進取的無限潛力,攜手大家一起走向共同輝煌的未來,回首過去,我們不會因為取得了一點點成績而沾沾自喜,相反的是面對競爭越來越激烈的市場氛圍,我們更要明確自己的不足,做好迎接新挑戰的準備,要不畏困難,激流勇進,以一個更嶄新的精神面貌迎接大家,共同走向輝煌回來!

- 吉林智能制造MES系統價格 2025-12-08

- 貴州高良率管控測試管理系統定制 2025-12-08

- 車間良率管理系統開發商 2025-12-08

- 寧夏國產良率管理系統解決方案 2025-12-08

- 安徽晶圓YMS服務商 2025-12-08

- 西藏可視化Mapping Inkless系統定制 2025-12-08

- 中國臺灣芯片YMS報價 2025-12-08

- 云南車間良率管理系統定制 2025-12-08

- 吉林自動化PAT工具 2025-12-08

- 安徽自動化Mapping Inkless解決方案 2025-12-07

- 山西小程序開發配置 2025-12-08

- 初中物理教師備課APP下載推薦 2025-12-08

- 徐州市數字化運輸管理系統試用 2025-12-08

- 云南出口智能硬件 2025-12-08

- 初中物理探究軟件排名 2025-12-08

- 西藏國產三維數字化移交 2025-12-08

- 天長創新型GEO優化專業服務商 2025-12-08

- 山東醫院移動款數字人價格 2025-12-08

- 安徽定制化觸控一體機展示互動效果 2025-12-08

- 黃浦區品牌數據定向分析 2025-12-08