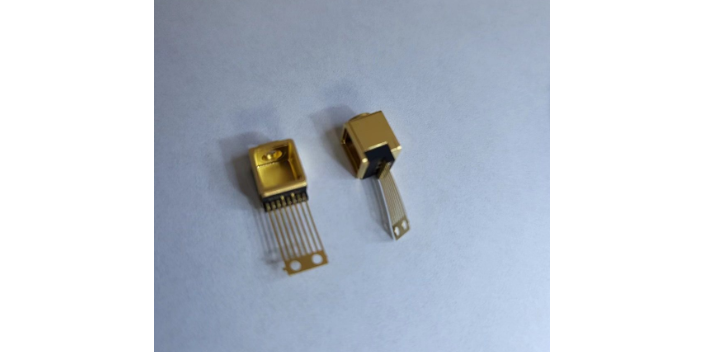

北京光學(xué)電子元器件鍍金銀

電子元件鍍金的前處理工藝與質(zhì)量保障,

前處理是電子元件鍍金質(zhì)量的基礎(chǔ),直接影響鍍層附著力與均勻性。工藝需分三步推進(jìn):首先通過超聲波脫脂(堿性脫脂劑,50-60℃,5-10min)處理基材表面油污、指紋,避免鍍層局部剝離;其次用 5%-10% 硫酸溶液酸洗活化,去除銅、鋁合金基材的氧化層,確保表面粗糙度 Ra≤0.2μm;預(yù)鍍 1-3μm 鎳層,作為擴(kuò)散屏障阻止基材金屬離子向金層遷移,同時增強(qiáng)結(jié)合力。同遠(yuǎn)表面處理對前處理質(zhì)量實行全檢,通過金相顯微鏡抽檢基材表面狀態(tài),對氧化層殘留、粗糙度超標(biāo)的工件立即返工,從源頭避免后續(xù)鍍層出現(xiàn)真、起皮等問題,使鍍金層剝離強(qiáng)度穩(wěn)定在 15N/cm 以上。 電子元器件鍍金需通過鹽霧、插拔測試,驗證鍍層耐磨損與穩(wěn)定性。北京光學(xué)電子元器件鍍金銀

電子元器件鍍金層的硬度與耐磨性優(yōu)化 電子元器件在裝配、使用過程中易因摩擦導(dǎo)致鍍金層磨損,影響性能,因此鍍層的硬度與耐磨性成為關(guān)鍵指標(biāo)。普通鍍金層硬度約150~200HV,耐磨性能較差,而同遠(yuǎn)表面處理通過技術(shù)創(chuàng)新,研發(fā)出加硬膜鍍金工藝:在鍍液中添加特殊合金元素,改變金層結(jié)晶結(jié)構(gòu),使鍍層硬度提升至800~2000HV;同時優(yōu)化沉積速率,形成致密的金層結(jié)構(gòu),減少孔隙率,進(jìn)一步增強(qiáng)耐磨性。為驗證性能,公司通過專業(yè)測試:對鍍金連接器進(jìn)行插拔磨損測試,經(jīng) 10000 次插拔后,鍍層磨損量<0.05μm,仍能維持良好導(dǎo)電性能;鹽霧測試中,鍍層在中性鹽霧環(huán)境下連續(xù)測試 500 小時無腐蝕痕跡。該工藝尤其適用于汽車電子、工業(yè)控制等高頻插拔、惡劣環(huán)境下使用的元器件,有效解決傳統(tǒng)鍍金層易磨損、壽命短的問題,為產(chǎn)品品質(zhì)保駕護(hù)航。貴州電容電子元器件鍍金鈀高頻元器件鍍金,有效減少信號衰減,提升性能。

陶瓷片的機(jī)械穩(wěn)定性直接關(guān)系到其在安裝、使用及環(huán)境變化中的可靠性,而鍍金層厚度通過影響鍍層與基材的結(jié)合狀態(tài)、應(yīng)力分布,對機(jī)械性能產(chǎn)生明顯調(diào)控作用,具體可從以下維度展開:

一、鍍層結(jié)合力:厚度影響界面穩(wěn)定性陶瓷與金的熱膨脹系數(shù)差異較大(陶瓷約 1-8×10??/℃,金約 14.2×10??/℃),厚度是決定兩者結(jié)合力的關(guān)鍵。

二、抗環(huán)境沖擊能力:厚度適配場景強(qiáng)度在潮濕、腐蝕性環(huán)境中,厚度直接影響鍍層的抗破損能力。厚度低于 0.6 微米的鍍層,孔隙率較高(每平方厘米>5 個),環(huán)境中的水汽、鹽分易通過孔隙滲透至陶瓷表面,導(dǎo)致界面氧化,使鍍層的抗彎折性能下降 —— 在 180° 彎折測試中,0.5 微米鍍層的斷裂概率達(dá) 30%,而 1.0 微米鍍層斷裂概率為 5%。

三、耐磨損性能:厚度決定使用壽命在需要頻繁插拔或接觸的場景(如陶瓷連接器),鍍層厚度與耐磨損壽命呈正相關(guān)。厚度0.8 微米的鍍層,在插拔測試(5000 次,插拔力 5-10N)后,鍍層磨損量約為 0.3 微米,仍能維持基礎(chǔ)導(dǎo)電與機(jī)械結(jié)構(gòu);而厚度1.2 微米的鍍層,可承受 10000 次以上插拔,磨損后剩余厚度仍達(dá) 0.5 微米,滿足工業(yè)設(shè)備 “百萬次壽命” 的設(shè)計需求。

鍍金層厚度對電子元件性能的具體影響

鍍金層厚度是決定電子元件性能與可靠性的重心參數(shù)之一,其對元件的導(dǎo)電穩(wěn)定性、耐腐蝕性、機(jī)械耐久性及信號傳輸質(zhì)量均存在直接且明顯的影響,從導(dǎo)電性能來看,鍍金層的重心優(yōu)勢是低電阻率(約 2.44×10??Ω?m),但厚度需達(dá)到 “連續(xù)成膜閾值”(通常≥0.1μm)才能發(fā)揮作用。在耐腐蝕性方面,金的化學(xué)惰性使其能隔絕空氣、濕度及腐蝕性氣體(如硫化物、氯化物),但防護(hù)能力完全依賴厚度。從機(jī)械與連接可靠性角度,鍍金層需兼顧 “耐磨性” 與 “結(jié)合力”。過薄鍍層(<0.1μm)在插拔、震動場景下(如連接器、按鍵觸點)易快速磨損,導(dǎo)致基材暴露,引發(fā)接觸不良;但厚度并非越厚越好,若厚度過厚(如>5μm 且未優(yōu)化鍍層結(jié)構(gòu)),易因金與基材(如鎳底鍍層)的熱膨脹系數(shù)差異,在溫度循環(huán)中產(chǎn)生內(nèi)應(yīng)力,導(dǎo)致鍍層開裂、脫落,反而降低元件可靠性。 儲能設(shè)備元件鍍金,降低電阻損耗,提升儲能效率。

電子元件鍍金厚度需根據(jù)應(yīng)用場景精細(xì)設(shè)計,避免過厚增加成本或過薄導(dǎo)致性能失效。消費電子輕載元件(如普通電阻、電容)常用 0.1-0.3μm 薄鍍層,以基礎(chǔ)防護(hù)為主,平衡成本與導(dǎo)電性;通訊連接器、工業(yè)傳感器需 0.5-2μm 中厚鍍層,保障插拔壽命與信號穩(wěn)定性,例如 5G 基站連接器鍍金層達(dá) 1μm 時,接觸電阻波動可控制在 5% 以內(nèi);航空航天、醫(yī)療植入設(shè)備則需 2-5μm 厚鍍層,應(yīng)對極端環(huán)境侵蝕,如心臟起搏器元件鍍金層達(dá) 3μm,可實現(xiàn) 15 年以上體內(nèi)穩(wěn)定工作。同遠(yuǎn)表面處理依托 X 射線熒光測厚儀與閉環(huán)控制系統(tǒng),將厚度公差控制在 ±0.1μm,滿足不同場景對鍍層厚度的差異化需求。

高頻雷達(dá)系統(tǒng)依賴低損耗信號傳輸,電子元器件鍍金通過優(yōu)化表面特性,滿足雷達(dá)性能需求。北京鍵合電子元器件鍍金

微型電子元件鍍金,在有限空間內(nèi)實現(xiàn)高效導(dǎo)電。北京光學(xué)電子元器件鍍金銀

電子元件鍍金的環(huán)保工藝與標(biāo)準(zhǔn)合規(guī)環(huán)保要求趨嚴(yán)下,電子元件鍍金工藝正向綠色化轉(zhuǎn)型。傳統(tǒng)青氣物鍍液因毒性大逐漸被替代,無氰鍍金工藝(如硫代硫酸鹽 - 亞硫酸鹽體系)成為主流,其金鹽利用率提升 20%,且符合 RoHS、EN1811 等國際標(biāo)準(zhǔn),廢水經(jīng)處理后重金屬排放量<0.1mg/L。同時,選擇性鍍金技術(shù)(如鎳禁止帶工藝)在元件關(guān)鍵觸點區(qū)域鍍金,減少金材損耗 30% 以上,降低資源浪費。同遠(yuǎn)表面處理通過鍍液循環(huán)過濾系統(tǒng)處理銅、鐵雜質(zhì)離子,搭配真空烘干技術(shù)減少能耗,全流程實現(xiàn) “零青氣物、低排放”,其環(huán)保鍍金工藝已通過 ISO 14001 認(rèn)證,適配汽車電子、兒童電子等對環(huán)保要求嚴(yán)苛的領(lǐng)域。北京光學(xué)電子元器件鍍金銀

- 云南電阻電子元器件鍍金銀 2025-12-08

- 江西電子元器件鍍金廠 2025-12-08

- 江西新能源電子元器件鍍金廠家 2025-12-08

- 清遠(yuǎn)氧化鋁陶瓷金屬化價格 2025-12-08

- 重慶電子元器件鍍金加工 2025-12-08

- HTCC電子元器件鍍金廠家 2025-12-07

- 北京光學(xué)電子元器件鍍金銀 2025-12-07

- 河北基板電子元器件鍍金鈀 2025-12-07

- 浙江電容電子元器件鍍金專業(yè)廠家 2025-12-07

- 廣東電子元器件鍍金銀 2025-12-07

- 廣東華大/小華電子元器件如何收費 2025-12-08

- 四川航空航天薄膜壓力傳感器生產(chǎn)廠家 2025-12-08

- 清遠(yuǎn)行業(yè)經(jīng)驗傳統(tǒng)骨架高技能團(tuán)隊保障 2025-12-08

- 湖南PCB抄板費用 2025-12-08

- 天津通用型變頻器銷售代理 2025-12-08

- 上海鎳銅合金電阻工藝 2025-12-08

- 精密耦合器代理商 2025-12-08

- 嘉定區(qū)什么是不銹鋼無縫管 2025-12-08

- 方言適配高性能離線語音芯片客服電話 2025-12-08

- 淮安什么是不銹鋼板 2025-12-08