能做sip封裝的廠家

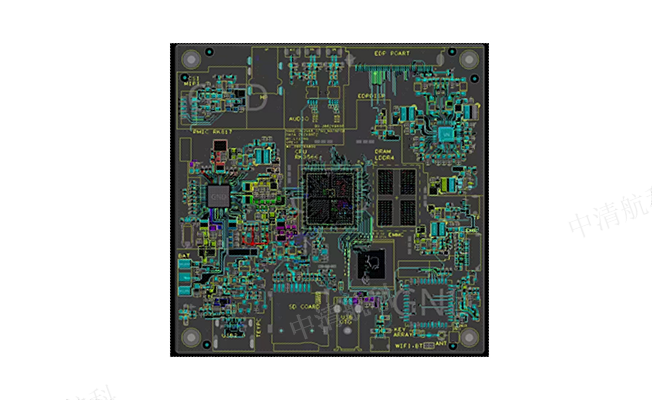

中清航科芯片封裝的應用領域-通信領域:在5G通信時代,對芯片的高速率、低延遲、高集成度等性能要求極高。中清航科憑借先進的芯片封裝技術,為5G基站的射頻芯片、基帶芯片等提供質優封裝服務,有效提升了芯片間的通信速度和數據處理能力,滿足了5G通信對高性能芯片的嚴苛需求,助力通信行業實現技術升級和網絡優化。中清航科芯片封裝的應用領域-消費電子領域:消費電子產品如智能手機、平板電腦、智能穿戴設備等,對芯片的尺寸、功耗和性能都有獨特要求。中清航科針對消費電子領域的特點,運用晶圓級封裝、系統級封裝等技術,為該領域客戶提供小型化、低功耗且高性能的芯片封裝解決方案,使消費電子產品在輕薄便攜的同時,具備更強大的功能和更穩定的性能。中清航科芯片封裝技術,平衡電氣性能與機械保護,延長芯片使用壽命。能做sip封裝的廠家

面對衛星載荷嚴苛的空間環境,中清航科開發陶瓷多層共燒(LTCC)MCM封裝技術。采用鎢銅熱沉基底與金錫共晶焊接,實現-196℃~+150℃極端溫變下熱失配率<3ppm/℃。通過嵌入式微帶線設計將信號串擾抑制在-60dB以下,使星載處理器在單粒子翻轉(SEU)事件率降低至1E-11errors/bit-day。該方案已通過ECSS-Q-ST-60-13C宇航標準認證,成功應用于低軌衛星星務計算機,模塊失效率<50FIT(10億小時運行故障率)。針對萬米級深海探測裝備的100MPa超高壓環境,中清航科金屬-陶瓷復合封裝結構。采用氧化鋯增韌氧化鋁(ZTA)陶瓷環與鈦合金殼體真空釬焊,實現漏率<1×10?1?Pa·m3/s的密封。內部壓力補償系統使腔體形變<0.05%,保障MEMS傳感器在110MPa壓力下精度保持±0.1%FS。耐腐蝕鍍層通過3000小時鹽霧試驗,已用于全海深聲吶陣列封裝,在馬里亞納海溝實現連續500小時無故障探測。上海fc-bga封裝基板超算芯片多芯片協同,中清航科先進封裝,降低芯片間數據傳輸延遲。

先進芯片封裝技術-晶圓級封裝(WLP):晶圓級封裝是在晶圓上進行封裝工藝,實現了芯片尺寸與封裝尺寸的接近,減小了封裝體積,提高了封裝密度。與傳統先切割晶圓再封裝不同,它是先封裝后切割晶圓。中清航科的晶圓級封裝技術處于行業前沿,能夠為客戶提供高集成度、小型化的芯片封裝產品,在物聯網、可穿戴設備等對芯片尺寸和功耗要求苛刻的領域具有廣闊應用前景。想要了解更多內容可以關注我司官網,另外有相關需求歡迎隨時聯系。

芯片封裝的環保要求:在環保意識日益增強的現在,芯片封裝生產也需符合環保標準。中清航科高度重視環境保護,在生產過程中采用環保材料、清潔能源和先進的廢氣、廢水處理技術,減少對環境的污染。公司嚴格遵守國家環保法規,通過了多項環保認證,實現了封裝生產與環境保護的協調發展,為客戶提供綠色、環保的封裝產品,助力客戶實現可持續發展目標。國際芯片封裝技術的發展趨勢:當前,國際芯片封裝技術呈現出集成化、小型化、高頻化、低功耗的發展趨勢。先進封裝技術如3DIC、Chiplet(芯粒)等成為研究熱點,這些技術能進一步提高芯片性能,降低成本。中清航科密切關注國際技術動態,與國際企業和研究機構保持合作交流,積極引進和吸收先進技術,不斷提升自身在國際市場的競爭力,為客戶提供與國際同步的先進封裝解決方案。中清航科芯片封裝技術,支持系統級封裝,實現芯片與被動元件一體化。

先進芯片封裝技術-2.5D/3D封裝:2.5D封裝技術可將多種類型芯片放入單個封裝,通過硅中介層實現信號橫向傳送,提升封裝尺寸和性能,需用到硅通孔(TSV)、重布線層(RDL)、微型凸塊等主要技術。3D封裝則是在垂直方向疊放兩個以上芯片,直接在芯片上打孔和布線連接上下層芯片堆疊,集成度更高。中清航科在2.5D/3D封裝技術方面持續創新,已成功應用于高性能計算、人工智能等領域,幫助客戶實現芯片性能的跨越式提升。有相關需求歡迎隨時聯系。芯片封裝需精密工藝,中清航科以創新技術提升散熱與穩定性,筑牢芯片性能基石。江蘇sot封裝加工

中清航科芯片封裝方案,適配物聯網設備,兼顧低功耗與小型化。能做sip封裝的廠家

中清航科部署封裝數字孿生系統,通過AI視覺檢測實現微米級缺陷捕捉。在BGA植球工藝中,球徑一致性控制±3μm,位置精度±5μm。智能校準系統使設備換線時間縮短至15分鐘,產能利用率提升至90%。針對HBM內存堆疊需求,中清航科開發超薄芯片處理工藝。通過臨時鍵合/解鍵合技術實現50μm超薄DRAM晶圓加工,4層堆疊厚度400μm。其TSV深寬比達10:1,阻抗控制在30mΩ以下,滿足GDDR6X1TB/s帶寬要求。中清航科可拉伸封裝技術攻克可穿戴設備難題。采用蛇形銅導線與彈性體基底結合,使LED陣列在100%拉伸形變下保持導電功能。醫療級生物相容材料通過ISO10993認證,已用于動態心電圖貼片量產。能做sip封裝的廠家

- 蘇州藍寶石晶圓切割 2025-12-07

- 徐州流片代理市場報價 2025-12-07

- 鹽城碳化硅線晶圓切割寬度 2025-12-06

- 上海sip多芯片封裝 2025-12-06

- 江蘇藍寶石晶圓切割企業 2025-12-06

- 紹興sic晶圓切割寬度 2025-12-06

- 江蘇第三代半導體封裝 2025-12-06

- 江蘇dil封裝管殼 2025-12-06

- 上海陶瓷封裝企業 2025-12-06

- 嘉興流片代理一般多少錢 2025-12-06

- 虎丘區現代智能倉儲管理系統 2025-12-07

- 浙江社交APP概念設計 2025-12-07

- 無錫什么文化藝術交流策劃 2025-12-07

- 山東多功能生產管理系統 2025-12-07

- 楊浦區OLED規定 2025-12-07

- 鄭州智能硬件 2025-12-07

- 安徽貿易文化藝術交流策劃 2025-12-07

- 天津各種市場營銷策劃 2025-12-07

- 遼寧智能墓區導航軟件護墓費 2025-12-07

- 杭州短視頻運營品牌企業 2025-12-07