溫州半導體刻蝕

這種方法的優點是刻蝕均勻性好,刻蝕側壁垂直,適合高分辨率和高深寬比的結構。缺點是刻蝕速率慢,選擇性低,設備復雜,成本高。混合法刻蝕:結合濕法和干法的優勢,采用交替或同時進行的濕法和干法刻蝕步驟,實現對氧化硅的高效、精確、可控的刻蝕。這種方法可以根據不同的應用需求,調節刻蝕參數和工藝條件,優化刻蝕結果。氧化硅刻蝕制程在半導體制造中有著廣泛的應用。例如:金屬-氧化物-半導體場效應晶體管(MOSFET):通過使用氧化硅刻蝕制程,在半導體襯底上形成柵極氧化層、源極/漏極區域、接觸孔等結構,實現MOSFET的功能;互連層:通過使用氧化硅刻蝕制程,在金屬層之間形成絕緣層、通孔、線路等結構,實現電路的互連。深硅刻蝕設備的工藝參數是指影響深硅刻蝕反應結果的各種因素。溫州半導體刻蝕

深硅刻蝕設備的未來展望是指深硅刻蝕設備在未來可能出現的新技術、新應用和新挑戰,它可以展示深硅刻蝕設備的創造潛力和發展方向。以下是一些深硅刻蝕設備的未來展望:一是新技術,即利用人工智能或機器學習等技術,實現深硅刻蝕設備的智能控制和自動優化,提高深硅刻蝕設備的生產效率和質量;二是新應用,即利用深硅刻蝕設備制造出具有新功能和新性能的硅結構,如可變形的硅結構、多層次的硅結構、多功能的硅結構等,拓展深硅刻蝕設備的應用領域和市場規模;三是新挑戰,即面對深硅刻蝕設備的環境影響、安全風險和成本壓力等問題,尋找更環保、更安全、更經濟的深硅刻蝕設備的解決方案,提高深硅刻蝕設備的社會責任和競爭力。溫州半導體刻蝕半導體介質層是指在半導體器件中用于隔離、絕緣、保護或調節電場的非導電材料層,如氧化硅、氮化硅等。

TSV制程是目前半導體制造業中為先進的技術之一,已經應用于很多產品生產。例如:CMOS圖像傳感器(CIS):通過使用TSV作為互連方式,可以實現背照式圖像傳感器(BSI)的設計,提高圖像質量和感光效率;三維封裝(3Dpackage):通過使用TSV作為垂直互連方式,可以實現不同功能和材料的芯片堆疊,提高系統性能和集成度;高帶寬存儲器(HBM):通過使用TSV作為內存模塊之間的互連方式,可以實現高密度、高速度、低功耗的存儲器解決方案。

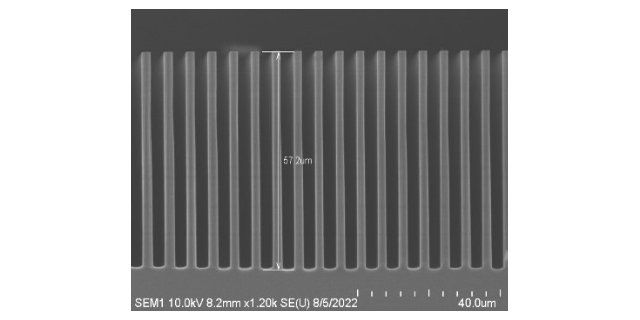

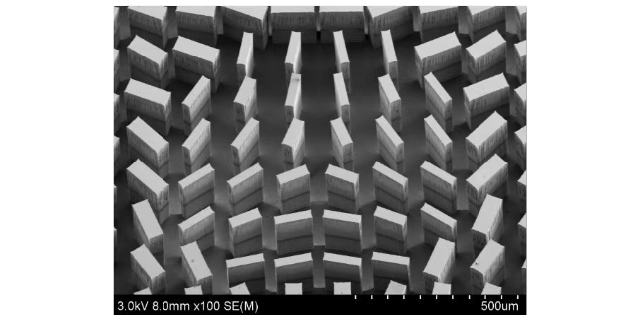

MEMS慣性傳感器領域依賴離子束刻蝕實現性能突破,其創新的深寬比控制技術解決高精度陀螺儀制造的痛點。通過建立雙離子源協同作用機制,在硅基底加工出深寬比超過25:1的微柱陣列結構。該工藝的重心突破在于發展出智能終端檢測系統與自補償算法,使諧振結構的熱漂移系數降至十億分之一級別,為自動駕駛系統提供超越衛星精度的慣性導航模塊。中性束刻蝕技術開啟介電材料加工新紀元,其獨特的粒子中性化機制徹底解決柵氧化層電荷損傷問題。在3nm邏輯芯片制造中,該技術創造性地保持原子級柵極界面完整性,使電子遷移率提升兩倍。主要技術突破在于發展出能量分散控制模塊,在納米鰭片加工中完美維持介電材料的晶體結構,為集成電路微縮提供原子級無損加工工藝路線。深硅刻蝕設備在半導體領域有著重要的應用,用于制造先進存儲器、邏輯器件等。

濕法刻蝕是較為原始的刻蝕技術,利用溶液與薄膜的化學反應去除薄膜未被保護掩模覆蓋的部分,從而達到刻蝕的目的。其反應產物必須是氣體或可溶于刻蝕劑的物質,否則會出現反應物沉淀的問題,影響刻蝕的正常進行。通常,使用濕法刻蝕處理的材料包括硅,鋁和二氧化硅等。二氧化硅的濕法刻蝕可以使用氫氟酸(HF)作為刻蝕劑,但是在反應過程中會不斷消耗氫氟酸,從而導致反應速率逐漸降低。為了避免這種現象的發生,通常在刻蝕溶液中加入氟化銨作為緩沖劑,形成的刻蝕溶液稱為BOE。氟化銨通過分解反應產生氫氟酸,維持氫氟酸的恒定濃度。深硅刻蝕設備在半導體領域有著重要的應用,主要用于制造先進存儲器、邏輯器件、射頻器件、功率器件等。溫州半導體刻蝕

根據TSV制程在芯片制造過程中的時序,可以將TSV分為三種類型。溫州半導體刻蝕

干法刻蝕設備根據不同的等離子體激發方式和刻蝕機理,可以分為以下幾種工藝類型:一是反應離子刻蝕(RIE),該類型是指利用射頻(RF)電源產生平行于電極平面的電場,從而激發出具有較高能量和方向性的離子束,并與自由基共同作用于樣品表面進行刻蝕。RIE類型具有較高的方向性和選擇性,但由于離子束對樣品表面造成較大的物理損傷和加熱效應,導致刻蝕速率較低、均勻性較差、荷載效應較大等缺點;二是感應耦合等離子體刻蝕(ICP),該類型是指利用射頻(RF)電源產生垂直于電極平面的電場,并通過感應線圈或天線將電場耦合到反應室內部,從而激發出具有較高密度和均勻性的等離子體,并通過另一個射頻(RF)電源控制樣品表面的偏置電壓,從而調節離子束的能量和方向性,并與自由基共同作用于樣品表面進行刻蝕。溫州半導體刻蝕

- 貴州晶圓鍵合服務 2025-12-08

- 江西表面活化晶圓鍵合廠商 2025-12-08

- 湖南高分辨電子束曝光加工工廠 2025-12-08

- 江西金屬晶圓鍵合實驗室 2025-12-06

- 浙江套刻電子束曝光服務 2025-12-06

- 吉林套刻電子束曝光加工 2025-12-06

- 福建表面活化晶圓鍵合加工 2025-12-06

- 遼寧微納光刻電子束曝光外協 2025-12-06

- 珠海精密加工電子束曝光工藝 2025-12-06

- 北京硅熔融晶圓鍵合價格 2025-12-06

- 新技術對RFID車間資產管理的影響 2025-12-08

- 杭州防爆電動閥品牌 2025-12-08

- 廣東華大/小華電子元器件如何收費 2025-12-08

- 四川航空航天薄膜壓力傳感器生產廠家 2025-12-08

- 清遠行業經驗傳統骨架高技能團隊保障 2025-12-08

- 湖南PCB抄板費用 2025-12-08

- 天津通用型變頻器銷售代理 2025-12-08

- 上海鎳銅合金電阻工藝 2025-12-08

- 精密耦合器代理商 2025-12-08

- 嘉定區什么是不銹鋼無縫管 2025-12-08