銀川多芯MT-FA光組件三維芯片互連技術

三維光子集成技術為多芯MT-FA光收發組件的性能突破提供了關鍵路徑。傳統二維平面集成受限于光子與電子元件的橫向排列密度,導致通道數量和能效難以兼顧。而三維集成通過垂直堆疊光子芯片與CMOS電子芯片,結合銅柱凸點高密度鍵合工藝,實現了80個光子通道在0.15mm2面積內的密集集成。這種結構使發射器單元的電光轉換能耗降至50fJ/bit,接收器單元的光電轉換能耗只70fJ/bit,較早期二維系統降低超80%。多芯MT-FA組件作為三維集成中的重要光學接口,其42.5°精密研磨端面與低損耗MT插芯的組合,確保了多路光信號在垂直方向上的高效耦合。通過將透鏡陣列直接貼合于FA端面,光信號可精確匯聚至光電探測器陣列,既簡化了封裝流程,又將耦合損耗控制在0.2dB以下。實驗數據顯示,采用三維集成的800G光模塊在持續運行中,MT-FA組件的通道均勻性波動小于0.1dB,滿足了AI算力集群對長期穩定傳輸的嚴苛要求。邊緣計算設備升級,三維光子互連芯片推動終端數據處理能力大幅提升。銀川多芯MT-FA光組件三維芯片互連技術

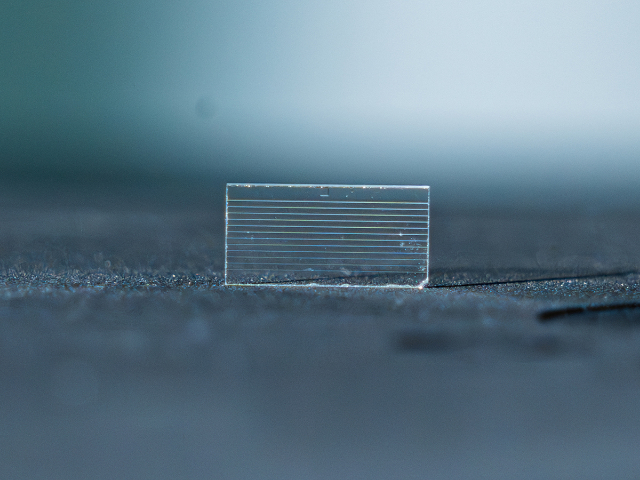

多芯MT-FA光組件在三維芯片架構中扮演著連接物理層與數據傳輸層的重要角色。三維芯片通過硅通孔(TSV)技術實現晶片垂直堆疊,將邏輯運算、存儲、傳感等異構功能模塊集成于單一封裝體內,但層間信號傳輸的帶寬與延遲問題始終制約其性能釋放。多芯MT-FA光組件憑借其高密度光纖陣列與精密研磨工藝,成為突破這一瓶頸的關鍵技術。其采用低損耗MT插芯與特定角度端面全反射設計,可在1.6T及以上速率的光模塊中實現多通道并行光信號傳輸,通道數可達24芯甚至更高。例如,在三維堆疊的HBM存儲器與AI加速卡互聯場景中,MT-FA組件通過緊湊的并行連接方案,將全局互連長度縮短2-3個數量級,使層間數據傳輸延遲降低50%以上,同時功耗減少30%。這種物理層的光互聯能力,與三維芯片的TSV電氣互連形成互補,構建起電-光-電混合傳輸架構,既利用了TSV在短距離內的低電阻優勢,又通過光信號的長距離、低損耗特性解決了層間跨芯片通信的瓶頸。成都多芯MT-FA光組件三維芯片傳輸技術三維光子互連芯片的拓撲優化設計,提升復雜結構的光傳輸效率。

三維光子互連芯片在數據中心、高性能計算(HPC)、人工智能(AI)等領域具有廣闊的應用前景。通過實現較低光信號損耗,可以明顯提升數據傳輸的速率和效率,降低系統的功耗和噪聲,為這些領域的發展提供強有力的技術支持。然而,三維光子互連芯片的發展仍面臨諸多挑戰,如工藝復雜度高、成本高昂、可靠性問題等。因此,需要持續投入研發力量,不斷優化技術方案,推動三維光子互連芯片的產業化進程。實現較低光信號損耗是提升三維光子互連芯片整體性能的關鍵。通過先進的光波導設計、高效的光信號復用技術、優化的光子集成工藝以及創新的片上光緩存和光處理技術,可以明顯降低光信號在傳輸過程中的損耗,提高數據傳輸的速率和效率。

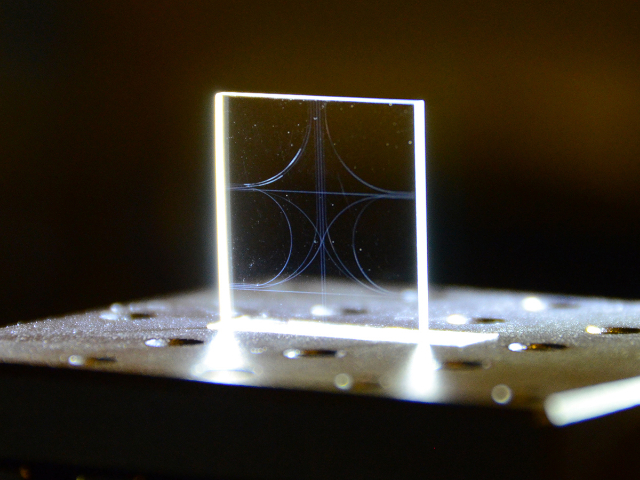

從工藝實現層面看,多芯MT-FA的制造涉及超精密加工、光學鍍膜、材料科學等多學科交叉技術。其重要工藝包括:采用五軸聯動金剛石車床對光纖陣列端面進行42.5°非球面研磨,表面粗糙度需控制在Ra<5nm;通過紫外固化膠水實現光纖與V槽的亞微米級定位,膠水收縮率需低于0.1%以避免應力導致的偏移;端面鍍制AR/HR增透膜,使1550nm波段反射率低于0.1%。在可靠性測試中,該連接器需通過85℃/85%RH高溫高濕試驗、500次插拔循環測試以及-40℃至85℃溫度沖擊試驗,確保在數據中心24小時不間斷運行場景下的穩定性。值得注意的是,多芯MT-FA的模塊化設計使其可兼容QSFP-DD、OSFP等主流光模塊接口標準,通過標準化插芯實現即插即用。隨著硅光集成技術的演進,未來多芯MT-FA將向更高密度發展,例如采用空芯光纖技術可將通道數擴展至72芯,同時通過3D打印技術實現定制化端面結構,進一步降低光子芯片的封裝復雜度。這種技術迭代不僅推動了光通信向1.6T及以上速率邁進,更為光子計算、量子通信等前沿領域提供了關鍵的基礎設施支撐。通過三維光子互連芯片,可以構建出高密度的光互連網絡,實現海量數據的快速傳輸與處理。

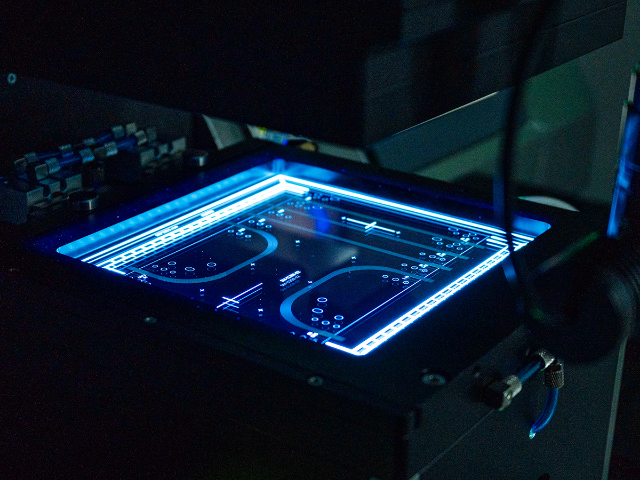

光子集成電路(Photonic Integrated Circuits, PICs)是將多個光子元件集成在一個芯片上的技術。三維設計在此領域的應用,使得研究人員能夠在單個芯片上構建多層光路網絡,明顯提升了集成密度和功能復雜性。例如,采用三維集成技術制造的硅基光子芯片,可以在極小的面積內集成數百個光子元件,極大地提高了數據處理能力。在光纖通訊系統中,三維設計可以幫助優化信號轉換節點的設計。通過使用三維封裝技術,可以將激光器、探測器以及其他無源元件緊密集成在一起,減少信號延遲并提高系統的整體效率。相比電子通信,三維光子互連芯片具有更低的功耗和更高的能效比。銀川多芯MT-FA光組件三維芯片互連技術

金融交易系統升級,三維光子互連芯片助力高頻交易數據的低延遲傳輸。銀川多芯MT-FA光組件三維芯片互連技術

該架構的突破性在于通過三維混合鍵合技術,將光子芯片與CMOS電子芯片的連接密度提升至每平方毫米2304個鍵合點,采用15μm間距的銅柱凸點陣列實現電-光-電信號的無縫轉換。在光子層,基于硅基微環諧振器的調制器通過垂直p-n結設計,使每伏特電壓產生75pm的諧振頻移,配合低電容(17fF)的鍺光電二極管,實現光信號到電信號的高效轉換;在電子層,級聯配置的高速晶體管與反相器跨阻放大器(TIA)協同工作,消除光電二極管電流的直流偏移,同時通過主動電感電路補償頻率限制。這種立體分層結構使系統在8Gb/s速率下保持誤碼率低于6×10??,且片上錯誤計數器顯示無錯誤傳輸。實際應用中,該架構已驗證在1.6T光模塊中支持200GPAM4信號傳輸,通過硅光封裝技術將組件尺寸縮小40%,功耗降低30%,滿足AI算力集群對高帶寬、低延遲的嚴苛需求。其多芯并行傳輸能力更使面板IO密度提升3倍以上,為下一代數據中心的光互連提供了可擴展的解決方案。銀川多芯MT-FA光組件三維芯片互連技術

- 寧波多芯MT-FA光組件三維芯片耦合技術 2025-12-06

- 北京多芯MT-FA扇入扇出代工 2025-12-06

- 多芯MT-FA光組件供應公司 2025-12-06

- 多芯MT-FA 1.6T/3.2T光模塊規格 2025-12-06

- 蘭州多芯MT-FA光組件在長距傳輸中的應用 2025-12-06

- 無錫多芯MT-FA光組件技術參數 2025-12-06

- 江蘇多芯MT-FA扇出組件定制 2025-12-06

- 重慶多芯MT-FA光纖連接器采購指南 2025-12-06

- 甘肅多芯MT-FA光組件價格 2025-12-06

- 溫州多芯MT-FA光組件 2025-12-06

- 車載定位器排名 2025-12-06

- 成都 技術成熟的國產交換芯片 2025-12-06

- 廣西車北斗視頻監控 2025-12-06

- 成都 低功耗國產交換芯片設計方案 2025-12-06

- 北海五類水晶頭 2025-12-06

- 韶關路由器水晶頭 2025-12-06

- 黑龍江多系統適配圖像標注優勢 2025-12-06

- 歐創車載定位器防丟 2025-12-06

- 電磁兼容信號源 2025-12-06

- 寧波多芯MT-FA光組件三維芯片耦合技術 2025-12-06