-

YuanStem 20多能干細(xì)胞培養(yǎng)基使用說明書

-

YuanStem 20多能干細(xì)胞培養(yǎng)基

-

YuanStem 8多能干細(xì)胞培養(yǎng)基

-

當(dāng)轉(zhuǎn)染變成科研的吞金獸,你還要忍多久?

-

ProFect-3K轉(zhuǎn)染挑戰(zhàn)賽—更接近Lipo3k的轉(zhuǎn)染試劑

-

自免/代謝/**/ADC——體內(nèi)中和&阻斷抗體

-

進(jìn)口品質(zhì)國(guó)產(chǎn)價(jià),科研試劑新**

-

腫瘤免疫研究中可重復(fù)數(shù)據(jù)的“降本增效”方案

-

Tonbo流式明星產(chǎn)品 流式抗體新選擇—高性價(jià)比的一站式服務(wù)

-

如何選擇合適的in vivo anti-PD-1抗體

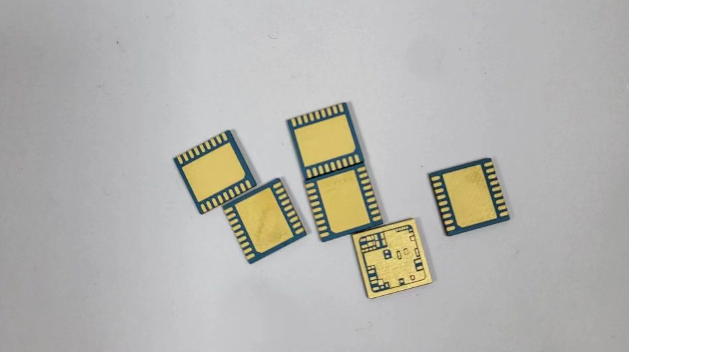

北京氧化鋁電子元器件鍍金鎳

電子元器件鍍金層常見失效原因分析 電子元器件鍍金產(chǎn)品在使用過程中可能出現(xiàn)失效情況,主要原因包括以下方面。首先是鍍金層自身結(jié)合力不足,鍍前處理環(huán)節(jié)若清洗不徹底,導(dǎo)致表面殘留油污、氧化物等雜質(zhì),或者鍍金工藝參數(shù)設(shè)置不合理,如電鍍液成分比例失調(diào)、溫度和電流密度控制不當(dāng),都將阻礙金層與基體的緊密結(jié)合,使得鍍金層在后續(xù)使用中容易出現(xiàn)起皮、脫落現(xiàn)象。 其次,鍍金層厚度不均勻或不足也會(huì)引發(fā)問題。在電鍍過程中,若電極布置不合理、溶液攪拌不均勻,會(huì)造成電子元器件表面不同部位的鍍金層厚度不一致。厚度不足的區(qū)域耐腐蝕性和耐磨性較差,在長(zhǎng)期使用或經(jīng)受物理、化學(xué)作用后,容易率先破損,使內(nèi)部金屬暴露,進(jìn)而引發(fā)失效。 再者,孔隙率過高也是常見問題。鍍金層存在孔隙會(huì)使底層金屬與外界環(huán)境接觸,容易發(fā)生腐蝕。孔隙率過高可能是由于鍍金工藝中電流密度過大、鍍液中添加劑使用不當(dāng)?shù)仍颍瑢?dǎo)致金層在生長(zhǎng)過程中形成不致密的結(jié)構(gòu)。為確保鍍金電子元器件的質(zhì)量和可靠性,必須對(duì)這些潛在的失效原因加以重視,并在生產(chǎn)過程中嚴(yán)格控制各個(gè)環(huán)節(jié) 。消費(fèi)電子追求小型化與長(zhǎng)壽命,電子元器件鍍金在縮小元件體積的同時(shí),延長(zhǎng)設(shè)備使用周期。北京氧化鋁電子元器件鍍金鎳

電子元件鍍金的前處理工藝與質(zhì)量保障,

前處理是電子元件鍍金質(zhì)量的基礎(chǔ),直接影響鍍層附著力與均勻性。工藝需分三步推進(jìn):首先通過超聲波脫脂(堿性脫脂劑,50-60℃,5-10min)處理基材表面油污、指紋,避免鍍層局部剝離;其次用 5%-10% 硫酸溶液酸洗活化,去除銅、鋁合金基材的氧化層,確保表面粗糙度 Ra≤0.2μm;預(yù)鍍 1-3μm 鎳層,作為擴(kuò)散屏障阻止基材金屬離子向金層遷移,同時(shí)增強(qiáng)結(jié)合力。同遠(yuǎn)表面處理對(duì)前處理質(zhì)量實(shí)行全檢,通過金相顯微鏡抽檢基材表面狀態(tài),對(duì)氧化層殘留、粗糙度超標(biāo)的工件立即返工,從源頭避免后續(xù)鍍層出現(xiàn)真、起皮等問題,使鍍金層剝離強(qiáng)度穩(wěn)定在 15N/cm 以上。 河北電阻電子元器件鍍金加工汽車電子元件需耐受振動(dòng)與溫度波動(dòng),電子元器件鍍金可增強(qiáng)結(jié)構(gòu)穩(wěn)定性,避免功能失效。

電子元器件鍍金需平衡精度與穩(wěn)定性,常見難點(diǎn)集中在微小元件的均勻鍍層控制。以 0.1mm 直徑的芯片引腳為例,傳統(tǒng)掛鍍易出現(xiàn)邊角鍍層過厚、中部偏薄的問題。同遠(yuǎn)通過研發(fā)旋轉(zhuǎn)式電鍍槽,使元件在鍍液中做 360 度勻速翻轉(zhuǎn),配合脈沖電流(頻率 500Hz)讓金離子均勻吸附,解決了厚度偏差超 10% 的行業(yè)痛點(diǎn)。針對(duì)高精密傳感器,其采用激光預(yù)處理技術(shù),在基材表面蝕刻納米級(jí)凹坑,使鍍層附著力提升 60%,經(jīng) 1000 次冷熱沖擊試驗(yàn)無(wú)脫落。此外,無(wú)氰鍍金工藝的突破,將鍍液毒性降低 90%,滿足歐盟 RoHS 新標(biāo)準(zhǔn)。

在電子元器件領(lǐng)域,鍍金工藝是保障設(shè)備性能的關(guān)鍵環(huán)節(jié),同遠(yuǎn)表面處理有限公司憑借精湛技術(shù)成為行業(yè)**。其鍍金精度堪稱一絕,X 射線測(cè)厚儀的應(yīng)用讓每層金厚誤差控制在 0.1 微米內(nèi),連精密儀器廠采購(gòu)都驚嘆 “堪比手術(shù)刀精度”。這種精細(xì)不僅體現(xiàn)在厚度上,更反映在金層結(jié)晶的規(guī)整度上,工程師通過調(diào)試電流頻率,讓金原子緊密排列,為航天元件定制的特殊方案更是嚴(yán)絲合縫。面對(duì)不同場(chǎng)景的嚴(yán)苛需求,同遠(yuǎn)總有應(yīng)對(duì)之策。針對(duì)汽車電子的耐腐要求,車間技術(shù)員添加特殊添加劑,使鍍金件輕松通過 96 小時(shí)鹽霧測(cè)試,即便模擬海水環(huán)境也完好如初;5G 設(shè)備商關(guān)注的耐磨與導(dǎo)電穩(wěn)定性,在這里也得到完美解決,鍍層結(jié)合力達(dá) 5N/cm2,插拔測(cè)試 5000 次后接觸電阻依舊穩(wěn)定,應(yīng)對(duì) 5 萬(wàn)次使用不在話下。成本控制上,同遠(yuǎn)同樣表現(xiàn)出色。自動(dòng)掛具的運(yùn)用讓每個(gè)元件均勻 “吃金”,較人工省料 30%,既保證質(zhì)量又降低消耗。從精密儀器到航天、汽車、5G 領(lǐng)域,同遠(yuǎn)以專業(yè)工藝為各類電子元器件賦能,彰顯了在電子元器件鍍金領(lǐng)域的硬實(shí)力。鍍金賦予電子元件優(yōu)導(dǎo)電與強(qiáng)抗腐性能。

電子元件鍍金厚度需根據(jù)應(yīng)用場(chǎng)景精細(xì)設(shè)計(jì),避免過厚增加成本或過薄導(dǎo)致性能失效。消費(fèi)電子輕載元件(如普通電阻、電容)常用 0.1-0.3μm 薄鍍層,以基礎(chǔ)防護(hù)為主,平衡成本與導(dǎo)電性;通訊連接器、工業(yè)傳感器需 0.5-2μm 中厚鍍層,保障插拔壽命與信號(hào)穩(wěn)定性,例如 5G 基站連接器鍍金層達(dá) 1μm 時(shí),接觸電阻波動(dòng)可控制在 5% 以內(nèi);航空航天、醫(yī)療植入設(shè)備則需 2-5μm 厚鍍層,應(yīng)對(duì)極端環(huán)境侵蝕,如心臟起搏器元件鍍金層達(dá) 3μm,可實(shí)現(xiàn) 15 年以上體內(nèi)穩(wěn)定工作。同遠(yuǎn)表面處理依托 X 射線熒光測(cè)厚儀與閉環(huán)控制系統(tǒng),將厚度公差控制在 ±0.1μm,滿足不同場(chǎng)景對(duì)鍍層厚度的差異化需求。

鍍金層薄卻耐用,適配電子元件小型化需求。河北陶瓷電子元器件鍍金專業(yè)廠家

工業(yè)控制設(shè)備長(zhǎng)期處于粉塵環(huán)境,電子元器件鍍金可隔絕污染物,防止元件接觸不良。北京氧化鋁電子元器件鍍金鎳

鍍金層厚度是決定陶瓷片導(dǎo)電性能的重心參數(shù),其影響并非線性關(guān)系,而是存在明確的閾值區(qū)間與性能拐點(diǎn),具體可從以下維度解析:

一、“連續(xù)鍍層閾值” 決定導(dǎo)電基礎(chǔ)陶瓷本身為絕緣材料(體積電阻率>101?Ω?cm),導(dǎo)電完全依賴鍍金層。

二、中厚鍍層實(shí)現(xiàn)高性能導(dǎo)電厚度在0.8-1.5 微米區(qū)間時(shí),鍍金層形成均勻致密的晶體結(jié)構(gòu),孔隙率降至每平方厘米<1 個(gè),表面電阻穩(wěn)定維持在 0.02-0.05Ω/□,且電阻溫度系數(shù)(TCR)低至 5×10??/℃以下,能在 - 60℃至 150℃的溫度范圍內(nèi)保持導(dǎo)電性能穩(wěn)定。

三、實(shí)際應(yīng)用中的厚度適配邏輯不同導(dǎo)電需求對(duì)應(yīng)差異化厚度選擇:低壓小電流場(chǎng)景(如電子標(biāo)簽天線):0.5-0.8 微米厚度,平衡成本與基礎(chǔ)導(dǎo)電需求;高頻信號(hào)傳輸場(chǎng)景(如雷達(dá)陶瓷組件):1.0-1.2 微米厚度,優(yōu)先保證低阻抗與穩(wěn)定性;高功率電極場(chǎng)景(如新能源汽車陶瓷電容):1.2-1.5 微米厚度,兼顧導(dǎo)電與抗燒蝕能力。 北京氧化鋁電子元器件鍍金鎳

- 珠海鍍鎳陶瓷金屬化處理工藝 2025-12-10

- 北京片式電子元器件鍍金貴金屬 2025-12-09

- 河北貼片電子元器件鍍金鈀 2025-12-09

- 廣東電容電子元器件鍍金鍍鎳線 2025-12-09

- 湖北電容電子元器件鍍金廠家 2025-12-09

- 陜西氧化鋁電子元器件鍍金銀 2025-12-09

- 湖北航天電子元器件鍍金鈀 2025-12-09

- 山東光學(xué)電子元器件鍍金專業(yè)廠家 2025-12-09

- 湖南片式電子元器件鍍金電鍍線 2025-12-09

- 重慶陶瓷金屬化封接 2025-12-09

- 寧波空調(diào)電動(dòng)閥型號(hào) 2025-12-10

- 江蘇高導(dǎo)電率母排生產(chǎn)廠家 2025-12-10

- 河南國(guó)產(chǎn)壓力分布檢測(cè)選型 2025-12-10

- 海南汽車部件EMC測(cè)試整改方案 2025-12-10

- 浙江耐高溫傳感器廠家現(xiàn)貨 2025-12-10

- 濟(jì)南光學(xué)傳感芯片MEMS微納加工長(zhǎng)期項(xiàng)目合作 2025-12-10

- 江蘇恒溫加熱PTC加熱片怎么樣 2025-12-10

- 色環(huán)電感是差模電感嗎 2025-12-10

- 佛山納米電子束曝光代工 2025-12-10

- 湖南傳感器電子元器件咨詢 2025-12-10