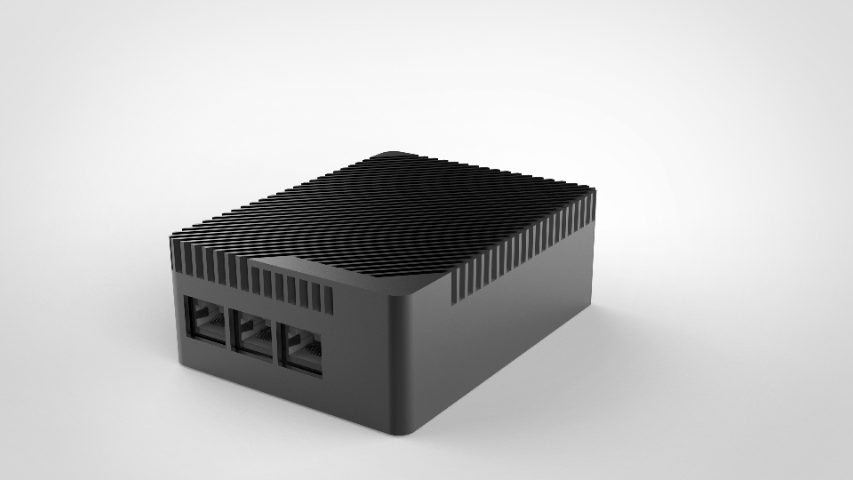

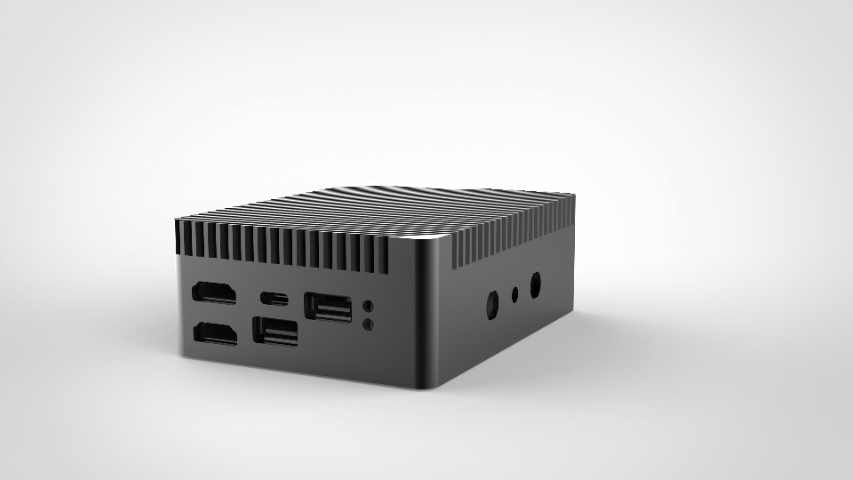

全場景定位位算單元平臺

位算單元與數據運算的準確性有著直接關聯。在計算機進行數值計算時,所有的十進制數都需要轉換為二進制數進行處理,而位算單元在轉換過程以及后續的運算過程中,都需要確保每一位二進制數據的運算結果準確無誤。一旦位算單元出現運算錯誤,可能會導致整個計算結果偏差,進而影響軟件程序的正常運行,甚至引發嚴重的系統故障。為了保障運算準確性,位算單元在設計階段會進行嚴格的邏輯驗證和測試,通過構建大量的測試用例,模擬各種復雜的運算場景,檢查位算單元在不同情況下的運算結果是否正確。同時,在實際應用中,部分處理器還會采用冗余設計,當主位算單元出現故障時,備用位算單元能夠及時接替工作,確保數據運算的連續性和準確性,這種設計在對可靠性要求極高的航空航天、醫療設備等領域尤為重要。在嵌入式系統中,位算單元降低了實時控制延遲。全場景定位位算單元平臺

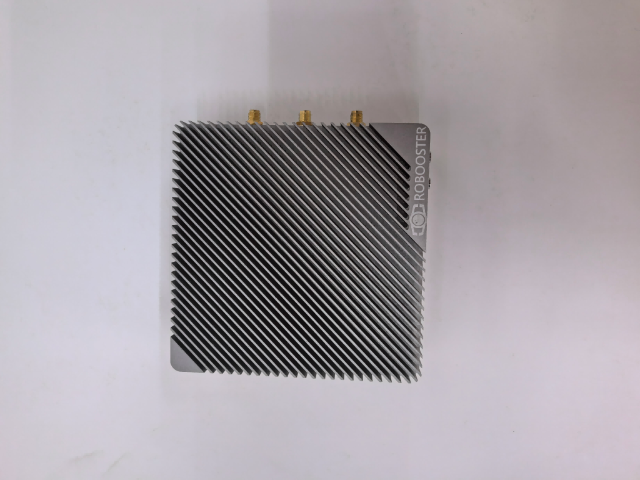

在通信技術領域,位算單元是實現數據傳輸和處理的關鍵部件。通信系統需要將數據轉換為適合傳輸的信號形式,并在接收端對信號進行解調和解碼,恢復出原始數據,這一過程涉及大量的位運算操作,需要位算單元高效完成。例如,在數字通信中的調制解調過程中,需要對數據進行編碼和譯碼,編碼過程中需要通過位運算將原始數據轉換為編碼序列,提高數據傳輸的抗干擾能力;譯碼過程中則需要通過位運算對接收的編碼序列進行處理,恢復出原始數據。在無線通信中,信號的濾波、變頻等處理也需要依賴位算單元進行大量的位運算,確保信號的質量和傳輸的穩定性。隨著 5G、6G 通信技術的發展,數據傳輸速率不斷提升,對通信設備中處理器的運算能力要求越來越高,位算單元需要具備更快的運算速度和更高的并行處理能力,以滿足高速數據傳輸和實時處理的需求。湖北智能制造位算單元廠家可重構計算中位算單元的靈活性如何實現?

位算單元的功耗與運算負載之間存在密切的關聯。位算單元的功耗主要包括動態功耗和靜態功耗,動態功耗是指位算單元在進行運算時,由于晶體管的開關動作產生的功耗,與運算負載的大小直接相關;靜態功耗是指位算單元在空閑狀態下,由于漏電流等因素產生的功耗,相對較為穩定。當位算單元的運算負載增加時,需要進行更多的晶體管開關動作,動態功耗會隨之增加;當運算負載減少時,動態功耗會相應降低。基于這一特性,設計人員可以通過動態調整位算單元的工作狀態,實現功耗的優化控制。例如,當運算負載較低時,降低位算單元的工作頻率或關閉部分空閑的運算模塊,減少動態功耗的消耗;當運算負載較高時,提高工作頻率或啟用更多的運算模塊,確保運算性能滿足需求。這種基于運算負載的動態功耗控制策略,能夠在保證位算單元運算性能的同時,較大限度地降低功耗,適用于對功耗敏感的移動設備、物聯網設備等場景。

編譯器是將高級語言(如C++、Python)轉化為機器指令的關鍵工具。而機器指令終由位算單元執行。優良的編譯器優化技術能夠生成更高效的指令序列,充分“壓榨”位算單元的性能潛力,減少空閑等待周期。因此,硬件設計師與軟件開發者需要共同協作,才能釋放位算單元的全部能量。雖然當前的位算單元處理的是經典二進制位(0或1),但未來的量子計算則基于量子比特(Qubit)。量子比特可以同時處于0和1的疊加態,其運算原理截然不同。然而,對量子邏輯門操作的理解,其靈感某種程度上也源于對經典位運算的深刻認知。二者將是未來計算科學相輔相成的兩大支柱。位算單元集成了ECC校驗模塊,提高數據可靠性。

從技術架構角度來看,位算單元的設計與計算機的整體性能密切相關。早期的位算單元多采用簡單的組合邏輯電路實現,雖然能夠完成基本的位運算,但在運算速度和并行處理能力上存在一定局限。隨著半導體技術的不斷發展,現代位算單元逐漸融入了流水線技術和并行處理架構。流水線技術可以將位運算的整個過程拆分為多個步驟,讓不同運算任務在不同階段同時進行,大幅提升了運算效率;并行處理架構則能夠讓位算單元同時對多組二進制數據進行運算,進一步增強了數據處理的吞吐量。此外,為了適應不同場景下的運算需求,部分高級處理器中的位算單元還支持可變位寬運算,既可以處理 8 位、16 位的短數據,也能夠應對 32 位、64 位的長數據,這種靈活性使得位算單元能夠更好地適配各種復雜的計算任務。位算單元支持多種位寬模式,適應不同應用場景。無錫全場景定位位算單元廠家

在圖像處理中,位算單元使二值化處理速度翻倍。全場景定位位算單元平臺

位算單元的物理實現需要考慮半導體制造工藝的特性,以確保性能與穩定性。不同的半導體制造工藝(如 28nm、14nm、7nm 等)在晶體管密度、開關速度、漏電流等方面存在差異,這些差異會直接影響位算單元的性能表現。在先進的制造工藝下,晶體管尺寸更小,位算單元能夠集成更多的運算模塊,同時運算速度更快、功耗更低;但先進工藝也面臨著漏電增加、工藝復雜度提升等挑戰,需要在設計中采取相應的優化措施。例如,在 7nm 工藝下設計位算單元時,需要采用更精細的電路布局,減少導線之間的寄生電容和電阻,降低信號延遲;同時采用多閾值電壓晶體管,在高頻運算模塊使用低閾值電壓晶體管提升速度,在靜態模塊使用高閾值電壓晶體管減少漏電流。此外,制造工藝的可靠性也需要重點關注,如通過冗余晶體管設計、抗老化電路等方式,應對工藝偏差和長期使用過程中的性能退化,確保位算單元在整個生命周期內穩定工作。全場景定位位算單元平臺

- 江蘇全場景定位位算單元售后 2025-11-06

- 山西高性能位算單元應用 2025-11-06

- 山西智能制造位算單元廠家 2025-11-06

- 山東機器人位算單元定制 2025-11-06

- 四川智能倉儲位算單元定制 2025-11-06

- 浙江全場景定位位算單元二次開發 2025-11-06

- 河北ROS位算單元廠家 2025-11-06

- 北京全場景定位位算單元 2025-11-06

- 無錫機器視覺位算單元廠家 2025-11-06

- 廣東位算單元哪家好 2025-11-06

- 激光皮帶輪對中檢測適應市場變化 2025-12-08

- 佛山4G水表采購 2025-12-08

- 安徽DDR3測試測試流程 2025-12-08

- 河南測距儀批發 2025-12-08

- 杭州轉子動平衡儀 2025-12-08

- 杭州閃爍氙燈光源定制 2025-12-08

- 成都***式編碼器 2025-12-08

- 電路板測溫型熱像儀價格 2025-12-08

- 四川布魯克顯微CT哪里好 2025-12-08

- 四川恒躍醫療耳鼻喉綜合工作臺設備 2025-12-08