山西位算單元哪家好

位算單元的并行處理能力對於提升大規(guī)模數(shù)據(jù)處理效率具有重要意義。隨著大數(shù)據(jù)技術的發(fā)展,需要處理的數(shù)據(jù)量呈指數(shù)級增長,傳統(tǒng)的串行運算方式已經(jīng)無法滿足數(shù)據(jù)處理的實時性需求,位算單元的并行處理能力成為關鍵。位算單元的并行處理能力主要體現(xiàn)在能夠同時對多組二進制數(shù)據(jù)進行運算,通過增加運算單元的數(shù)量或采用并行架構設計,實現(xiàn)多任務的同步處理。例如,在大數(shù)據(jù)分析中的數(shù)據(jù)篩選和排序操作中,位算單元可以同時對多組數(shù)據(jù)進行位運算比較,快速篩選出符合條件的數(shù)據(jù)并完成排序,大幅縮短數(shù)據(jù)處理時間;在分布式計算中,多個節(jié)點的位算單元可以同時處理不同的數(shù)據(jù)塊,通過協(xié)同工作完成大規(guī)模的數(shù)據(jù)運算任務。為了進一步提升并行處理能力,現(xiàn)代位算單元還會采用向量處理技術、SIMD(單指令多數(shù)據(jù))架構等,能夠在一條指令的控制下,同時對多個數(shù)據(jù)元素進行運算,進一步提高數(shù)據(jù)處理的吞吐量。光子計算技術會如何改變位算單元形態(tài)?山西位算單元哪家好

位算單元在虛擬現(xiàn)實(VR)和增強現(xiàn)實(AR)技術中發(fā)揮著重要作用。VR/AR 技術需要實時處理大量的圖像、音頻和傳感器數(shù)據(jù),生成沉浸式的虛擬環(huán)境或疊加虛擬信息到現(xiàn)實環(huán)境中,這一過程需要處理器具備強大的實時運算能力,位算單元作為關鍵運算部件,能夠高效完成相關的位運算任務。例如,在 VR 設備中,需要根據(jù)用戶的頭部運動數(shù)據(jù)實時調整虛擬場景的視角,傳感器采集的頭部運動數(shù)據(jù)轉換為二進制后,位算單元快速對數(shù)據(jù)進行位運算處理,計算出視角調整參數(shù),并傳遞給圖形渲染模塊,確保虛擬場景的實時更新,避免畫面延遲導致的眩暈感;在 AR 設備中,需要對攝像頭采集的現(xiàn)實場景圖像進行識別和跟蹤,位算單元通過位運算對圖像特征進行提取和匹配,實現(xiàn)對現(xiàn)實物體的精確識別和虛擬信息的精確疊加。位算單元的高效運算能力,為 VR/AR 技術的實時性和沉浸式體驗提供了關鍵支持,推動了 VR/AR 技術在游戲、教育、醫(yī)療、工業(yè)等領域的應用。無錫定位軌跡位算單元平臺位算單元的并行計算能力如何量化評估?

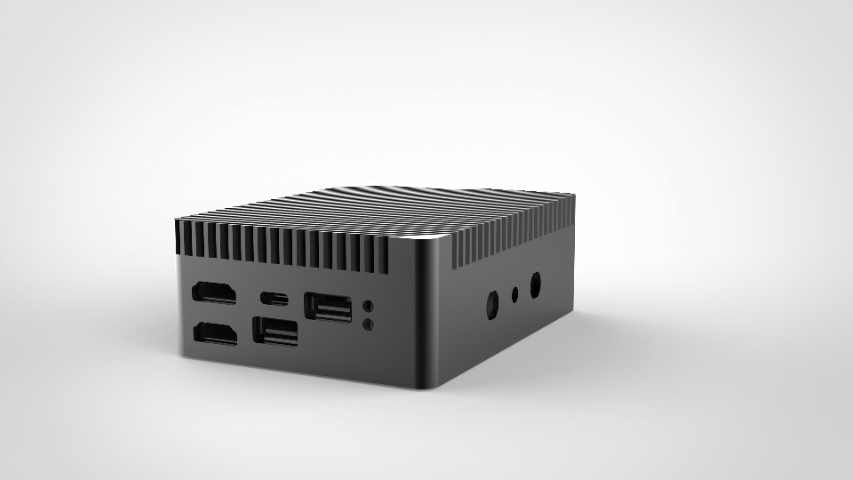

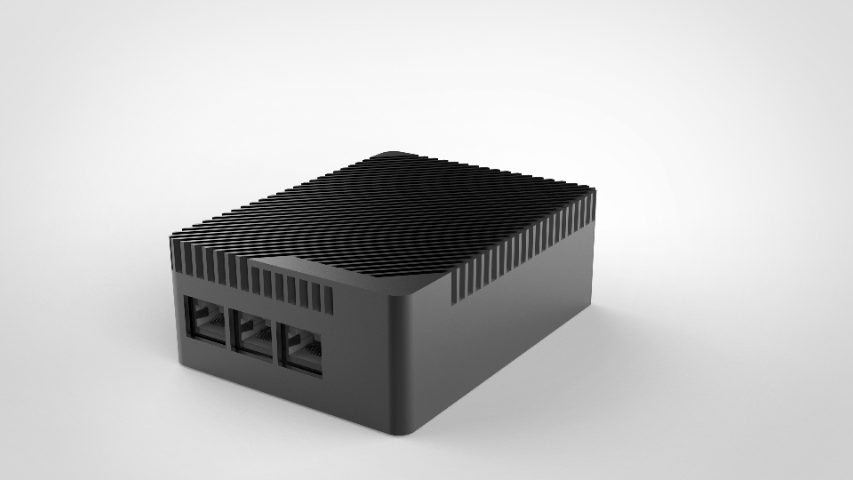

在嵌入式系統(tǒng)領域,位算單元的作用同樣不可忽視。嵌入式系統(tǒng)通常具有體積小、功耗低、功能專一的特點,廣泛應用于智能家居、汽車電子、工業(yè)控制等領域。在這些系統(tǒng)中,處理器需要頻繁處理各類傳感器采集的數(shù)據(jù),并根據(jù)數(shù)據(jù)結果執(zhí)行相應的控制指令,而位算單元在此過程中承擔著快速數(shù)據(jù)處理的重任。例如,在汽車電子的防抱死制動系統(tǒng)(ABS)中,傳感器會實時采集車輪的轉速數(shù)據(jù),這些數(shù)據(jù)以二進制形式傳輸?shù)教幚砥骱螅凰銌卧獣杆賹?shù)據(jù)進行位運算處理,判斷車輪是否有抱死的趨勢,并將處理結果傳遞給控制單元,從而及時調整制動壓力,保障行車安全。由于嵌入式系統(tǒng)對功耗和響應速度要求較高,位算單元在設計時往往會采用低功耗電路結構,并優(yōu)化運算流程,以在保證運算速度的同時,極大限度降低功耗。

傳統(tǒng)計算中,數(shù)據(jù)需要在處理器和內存之間頻繁搬運,消耗大量時間和能量。內存計算是一種新興架構,它將位算單元直接嵌入到內存陣列中,允許在數(shù)據(jù)存儲的位置直接進行計算。這種架構極大地減少了數(shù)據(jù)移動,特別適合數(shù)據(jù)密集型的應用,有望突破“內存墻”瓶頸,實現(xiàn)變革性的能效提升。并非所有應用都需要100%精確的計算結果。例如,圖像和音頻處理、機器學習推理等對微小誤差不敏感。近似計算技術通過設計可以容忍一定誤差的位算單元,來換取速度、面積或能耗上的大幅優(yōu)化。這種“夠用就好”的設計哲學,為在資源受限環(huán)境下提升性能提供了新穎的思路。新興應用對位算單元提出哪些新需求?

位算單元的功耗與運算負載之間存在密切的關聯(lián)。位算單元的功耗主要包括動態(tài)功耗和靜態(tài)功耗,動態(tài)功耗是指位算單元在進行運算時,由于晶體管的開關動作產(chǎn)生的功耗,與運算負載的大小直接相關;靜態(tài)功耗是指位算單元在空閑狀態(tài)下,由于漏電流等因素產(chǎn)生的功耗,相對較為穩(wěn)定。當位算單元的運算負載增加時,需要進行更多的晶體管開關動作,動態(tài)功耗會隨之增加;當運算負載減少時,動態(tài)功耗會相應降低。基于這一特性,設計人員可以通過動態(tài)調整位算單元的工作狀態(tài),實現(xiàn)功耗的優(yōu)化控制。例如,當運算負載較低時,降低位算單元的工作頻率或關閉部分空閑的運算模塊,減少動態(tài)功耗的消耗;當運算負載較高時,提高工作頻率或啟用更多的運算模塊,確保運算性能滿足需求。這種基于運算負載的動態(tài)功耗控制策略,能夠在保證位算單元運算性能的同時,較大限度地降低功耗,適用于對功耗敏感的移動設備、物聯(lián)網(wǎng)設備等場景。

如何設計位算單元的容錯機制?無錫定位軌跡位算單元平臺

存內計算架構如何重構位算單元設計?山西位算單元哪家好

位算單元的電磁兼容性設計是確保其在復雜環(huán)境中穩(wěn)定工作的重要保障。電磁兼容性(EMC)指設備或系統(tǒng)在電磁環(huán)境中能夠正常工作,且不對其他設備或系統(tǒng)造成電磁干擾的能力。位算單元作為處理器的關鍵模塊,在工作過程中會產(chǎn)生電磁輻射,同時也容易受到外部電磁干擾的影響,因此需要進行專門的電磁兼容性設計。在硬件設計層面,通過優(yōu)化電路布局,減少信號線的長度和交叉,降低電磁輻射;采用屏蔽措施,如在關鍵電路周圍設置金屬屏蔽層,阻擋外部電磁干擾;合理設計電源和接地系統(tǒng),減少電源噪聲對電路的影響。在 PCB(印制電路板)設計中,通過控制走線的阻抗、間距,避免信號反射和串擾,提升電路的抗干擾能力。此外,還需要通過電磁兼容性測試,模擬實際應用中的電磁環(huán)境,檢測位算單元的電磁輻射水平和抗干擾能力,確保其符合相關的電磁兼容性標準(如 CE、FCC 認證標準),避免因電磁干擾導致位算單元運算錯誤或性能下降。山西位算單元哪家好

- 江蘇全場景定位位算單元售后 2025-11-06

- 山西高性能位算單元應用 2025-11-06

- 山西智能制造位算單元廠家 2025-11-06

- 山東機器人位算單元定制 2025-11-06

- 四川智能倉儲位算單元定制 2025-11-06

- 浙江全場景定位位算單元二次開發(fā) 2025-11-06

- 河北ROS位算單元廠家 2025-11-06

- 北京全場景定位位算單元 2025-11-06

- 無錫機器視覺位算單元廠家 2025-11-06

- 廣東位算單元哪家好 2025-11-06

- 青海震蕩箱怎么選 2025-12-07

- 廣東全自動維氏硬度計布洛維 2025-12-07

- 熒光酶標儀毒性檢測 2025-12-07

- 陜西HR-150硬度計價格 2025-12-07

- 閔行區(qū)常用金屬材料銷售維保 2025-12-07

- 江蘇中低壓快速制備液相色譜大概價格多少 2025-12-07

- 山東怎樣選擇實驗室超純水設備服務熱線 2025-12-07

- 江蘇國內RPS冗余電源 2025-12-07

- 廣州油液激光粒子計數(shù)器選型 2025-12-07

- 蘇州特色服務霧化儀維保 2025-12-07