長沙Linux位算單元應用

位算單元是構建算術邏輯單元(ALU)的主要積木。一個完整的ALU通常包含多個位算單元,共同協作以執行完整的整數運算。可以將ALU視為一個團隊,而每一位算單元則是團隊中專注特定任務的隊員。它們并行工作,有的負責加法進位鏈,有的處理邏輯比較,協同輸出結果。因此,位算單元的性能優化,是提升整個ALU乃至CPU算力直接的途徑之一。人工智能,尤其是神經網絡推理,本質上是海量乘加運算的非線性組合。這些運算都會分解為基本的二進制操作。專為AI設計的加速器(如NPU、TPU)內置了經過特殊優化的位算單元陣列,它們針對低精度整數量化(INT8、INT4)模型進行了精致優化,能夠以極高的能效比執行推理任務,讓AI算法在終端設備上高效運行成為現實。新興應用對位算單元提出哪些新需求?長沙Linux位算單元應用

位算單元的故障容錯技術是提高處理器可靠性的重要保障。在一些對可靠性要求極高的領域,如航空航天、醫療設備、工業控制等,即使位算單元出現輕微故障,也可能導致嚴重的后果,因此需要采用故障容錯技術,確保位算單元在出現故障時仍能正常工作或極小化故障影響。位算單元常用的故障容錯技術包括冗余設計、錯誤檢測與糾正(EDC/ECC)技術等。冗余設計是指在處理器中設置多個相同的位算單元,當主位算單元出現故障時,備用位算單元能夠立即接替工作,保證運算的連續性;錯誤檢測與糾正技術則是通過在數據中添加冗余校驗位,位算單元在運算過程中對數據進行校驗,檢測出數據傳輸或運算過程中出現的錯誤,并通過校驗位進行糾正。例如,在采用 ECC 內存的系統中,位算單元在處理內存中的數據時,能夠通過 ECC 校驗技術檢測并糾正單比特錯誤,避免錯誤數據影響運算結果。這些故障容錯技術的應用,大幅提高了位算單元的可靠性,滿足了高可靠性領域的應用需求。合肥低功耗位算單元應用3D堆疊技術如何提升位算單元的性能密度?

在數據安全領域,位算單元發揮著關鍵作用。數據加密是保障信息安全的重要手段,而許多加密算法,如 AES 加密算法、RSA 加密算法等,都依賴位算單元進行復雜的位運算來實現數據的加密和解鎖過程。例如,在 AES 加密算法中,需要對數據進行字節代換、行移位、列混合和輪密鑰加等操作,其中列混合操作就涉及大量的位運算,位算單元需要快速完成這些運算,才能確保加密過程的高效進行。此外,在數字簽名和身份認證過程中,也需要通過位算單元對數據進行哈希運算和簽名驗證,以防止數據被篡改和偽造。為了提升數據安全處理的效率,部分處理器會集成專門的加密加速模塊,這些模塊本質上是優化后的位算單元,能夠針對特定的加密算法快速執行位運算,在保障數據安全的同時,減少對處理器主算力的占用。

位算單元在科學計算領域中是實現復雜數值計算的基礎,支撐科研工作的開展。科學計算涉及氣象預測、地質勘探、量子物理、生物信息學等多個領域,這些領域的計算任務往往具有數據量大、計算復雜度高的特點,需要依賴計算機進行高精度的數值運算,而位算單元則是這些運算的底層支撐。例如,在氣象預測中,需要對大氣運動方程進行求解,過程中涉及大量的矩陣運算和微分方程計算,這些計算終會分解為二進制位的運算,由位算單元高效執行,以快速生成氣象預測模型;在生物信息學中,對位基因序列的比對和分析需要處理海量的堿基對數據,位算單元通過位運算快速對比不同基因序列的二進制編碼,找出相似性和差異性,為基因研究提供數據支持。科學計算對運算精度和速度要求極高,位算單元通過與浮點運算單元等其他模塊的協同工作,能夠實現高精度的數值計算,同時通過并行處理技術提升運算速度,縮短科研項目的計算周期,推動科研成果的快速產出。通過增加位算單元的數量,處理器的位處理能力明顯增強。

在消費電子領域,位算單元的性能提升推動了產品功能的升級。消費電子產品如智能手機、平板電腦、智能電視等,其功能的豐富性和性能的優劣與處理器中的位算單元密切相關。隨著位算單元運算速度的提升和功能的拓展,消費電子產品能夠實現更多復雜的功能。例如,在智能手機的攝影功能中,需要對圖像進行自動對焦、曝光控制、圖像降噪、美顏處理等,這些功能的實現需要大量的位運算,位算單元的高效運算能夠讓手機快速完成圖像處理,提升拍照效果和成像速度;在智能電視的 4K、8K 視頻播放中,需要對視頻數據進行解碼和渲染,位算單元能夠快速完成視頻數據的位運算處理,確保視頻播放的流暢性和畫面質量。此外,消費電子產品的游戲性能也與位算單元密切相關,位算單元能夠快速處理游戲中的圖形渲染、物理引擎計算等任務,為用戶提供流暢的游戲體驗。位算單元的持續升級,為消費電子產品的功能創新和性能提升提供了有力支撐。如何驗證位算單元的功能完備性?蘇州定位軌跡位算單元系統

異構計算架構中位算單元的角色定位?長沙Linux位算單元應用

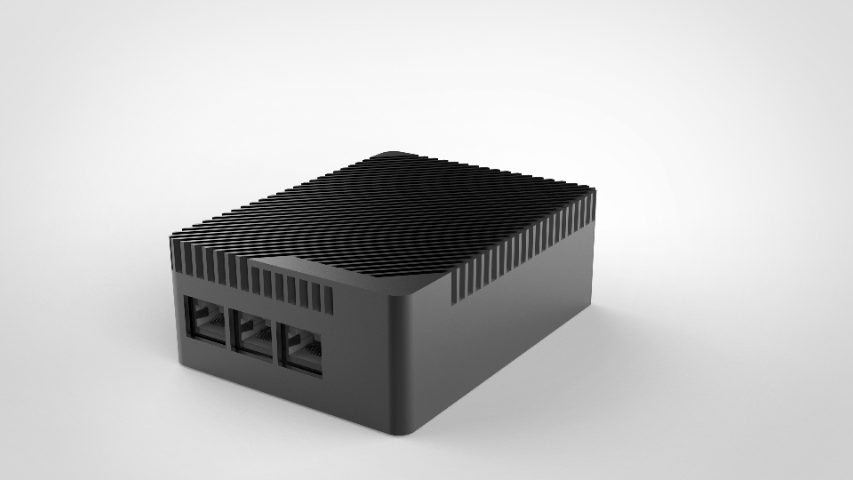

位算單元的電磁兼容性設計是確保其在復雜環境中穩定工作的重要保障。電磁兼容性(EMC)指設備或系統在電磁環境中能夠正常工作,且不對其他設備或系統造成電磁干擾的能力。位算單元作為處理器的關鍵模塊,在工作過程中會產生電磁輻射,同時也容易受到外部電磁干擾的影響,因此需要進行專門的電磁兼容性設計。在硬件設計層面,通過優化電路布局,減少信號線的長度和交叉,降低電磁輻射;采用屏蔽措施,如在關鍵電路周圍設置金屬屏蔽層,阻擋外部電磁干擾;合理設計電源和接地系統,減少電源噪聲對電路的影響。在 PCB(印制電路板)設計中,通過控制走線的阻抗、間距,避免信號反射和串擾,提升電路的抗干擾能力。此外,還需要通過電磁兼容性測試,模擬實際應用中的電磁環境,檢測位算單元的電磁輻射水平和抗干擾能力,確保其符合相關的電磁兼容性標準(如 CE、FCC 認證標準),避免因電磁干擾導致位算單元運算錯誤或性能下降。長沙Linux位算單元應用

- 江蘇全場景定位位算單元售后 2025-11-06

- 山西高性能位算單元應用 2025-11-06

- 山西智能制造位算單元廠家 2025-11-06

- 山東機器人位算單元定制 2025-11-06

- 四川智能倉儲位算單元定制 2025-11-06

- 浙江全場景定位位算單元二次開發 2025-11-06

- 河北ROS位算單元廠家 2025-11-06

- 北京全場景定位位算單元 2025-11-06

- 無錫機器視覺位算單元廠家 2025-11-06

- 廣東位算單元哪家好 2025-11-06

- 威海研究無創睡眠監測系統 2025-12-10

- 云南游離氯分析儀表電話 2025-12-10

- 網絡基礎設施監控 2025-12-10

- 杭州灌溉行業電磁流量計 2025-12-10

- 鹽城應用廣恒溫箱商家 2025-12-10

- 合肥品牌船舶自動化監測報警系統市場價 2025-12-10

- 珠海傳感器廠家價格 2025-12-10

- 嘉定區節能溢流閥調整 2025-12-10

- 杭州隔離型差壓變送器 2025-12-10

- 鎮江工廠冷熱沖擊試驗箱哪里有賣的 2025-12-10