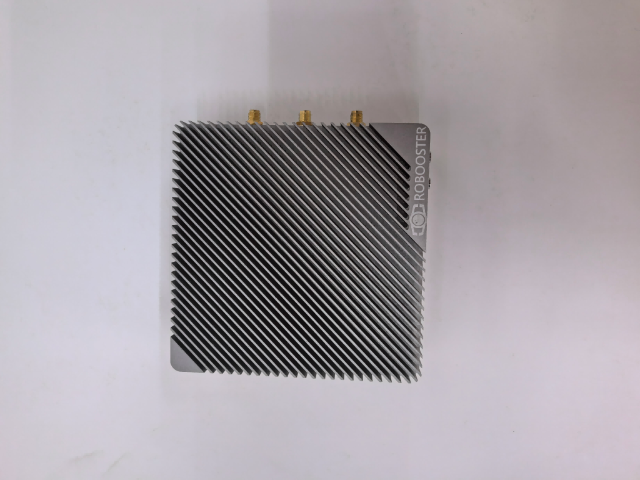

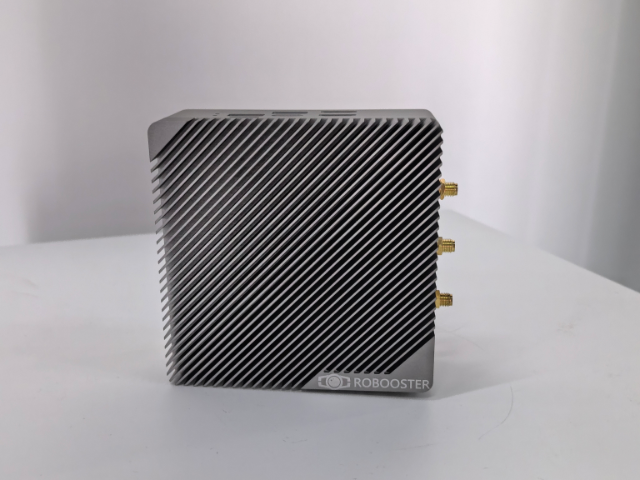

湖南工業級位算單元

量子計算與經典位運算的協同是當前量子信息技術發展的主要范式之一,兩者通過優勢互補實現復雜問題的高效求解。這種協同不僅體現在硬件架構的深度耦合,更貫穿于算法設計、控制邏輯與數據處理的全鏈條。這種協同模式在當前 “噪聲中等規模量子(NISQ)” 時代尤為關鍵 —— 據 IBM 測算,純量子計算在 40 量子比特以上的糾錯成本將超過問題本身價值,而混合架構可使有效量子比特數提升 3-5 倍。未來,隨著量子糾錯技術的突破,兩者將進一步融合為 “自洽的量子 - 經典計算棧”,推動人類算力進入新紀元。如何降低位算單元的功耗同時保持性能?湖南工業級位算單元

位算單元(Bitwise Operation Unit)是數字電路中執行按位運算的主要組件,支持與(AND)、或(OR)、非(NOT)、異或(XOR)等邏輯操作。它直接對二進制數據的每一位進行分開處理,不涉及算術進位,因此速度極快。位算單元用于處理器ALU(算術邏輯單元)、加密算法、圖像處理等領域,是高效數據處理的基石。相比算術運算,位算無需處理進位鏈,延遲更低。例如,用左移代替乘法(x << 3等效于x * 8)可大幅提升性能,因此在嵌入式系統和實時系統中應用。無錫機器視覺位算單元咨詢位算單元的性能功耗比優于傳統ALU設計。

位算單元作為低功耗傳感器控制的基石。低功耗協處理器的協同計算低功耗協處理器(如ESP32的ULP)通過位運算實現傳感器數據的本地處理,避免主MCU頻繁喚醒。例如:ULP 協處理器通過位操作(如(adc_value >> 12) & 0x0F)提取 ADC 采樣值的高 4 位,判斷溫度是否超限,只在觸發條件時喚醒主 MCU。運動傳感器的姿態識別(如步數統計)通過位并行算法(如二值化加速度數據后進行位與運算),在協處理器上完成,功耗可降低至主 MCU 的 1/10。內存與寄存器的高效利用位運算減少對外部內存的依賴,充分利用片上資源。例如:傳感器校準參數(如偏移量、增益系數)通過位掩碼(如offset=(calib_reg&0xFF00)>>8)直接從寄存器讀取,避免存儲到SRAM。狀態機設計中,位運算(如state=(state<<1)|sensor_flag)將多個傳感器狀態壓縮到一個字節,節省內存空間。

位算單元在圖形處理中發揮著重要作用,特別是在像素級操作、顏色處理和性能優化方面。以下是位運算在圖形處理中的關鍵應用。像素顏色操作:ARGB/RGBA顏色分量提取、ARGB/RGBA顏色組合。圖像混合與合成:Alpha混合(透明混合)。圖像濾鏡與優化:快速灰度轉換、亮度調整。圖像數據優化:內存對齊訪問、快速像素拷貝。 位圖(Bitmap)操作:透明通道處理、掩碼操作。位運算在圖形處理中的優勢在于:極高的執行效率(通常只需1-3個CPU周期)、避免浮點運算和類型轉換、可并行處理多個像素分量、減少內存訪問次數。位算單元的并行計算能力如何量化評估?

在現代CPU中,位算單元是算術邏輯單元(ALU)的重要組成部分,通常與加法器、乘法器等并行設計。由于其低延遲特性,位操作在底層編程(如嵌入式系統、驅動開發)中大量用于寄存器配置、標志位管理和數據壓縮。在處理器設計中,位算單元通常由邏輯門(如NAND、NOR)組合實現。例如,一個AND門可由兩個晶體管構成,而多位數操作通過并行邏輯門陣列完成。現代CPU采用流水線技術,將位操作指令與其他指令并行執行,以提升吞吐量。SIMD指令集(如IntelAVX、ARMNEON)進一步擴展了位算單元的并行能力,允許單條指令對128位或256位數據同時執行按位操作,明顯加速多媒體處理和科學計算。新型位算單元采用3D堆疊技術,密度提升50%。內蒙古高性能位算單元廠家

通過增加位算單元的數量,處理器的位處理能力明顯增強。湖南工業級位算單元

位算單元重構工業物聯網的實時性與能效邊界。位算單元(Bitwise Arithmetic Unit)在工業物聯網(IIoT)中扮演著實時性保障、能效優化與數據處理關鍵引擎的角色,其對二進制位的直接操作能力與工業場景的嚴苛需求高度契合。位算單元通過高速并行性、低功耗特性、位級操作靈活性,從傳感器數據采集到工業協議傳輸全鏈路優化工業物聯網的能效與實時性。其影響不僅體現在硬件寄存器的直接控制(如低功耗模式配置),更深入到算法設計(如設備故障特征提取)和系統架構(如邊緣 - 云端協同)。在工業 4.0 與智能制造的浪潮中,位算單元與工業物聯網的深度集成將持續推動設備向更小體積、更低功耗、更高可靠性的方向發展,成為工業數字化轉型的關鍵基石。湖南工業級位算單元

- 江蘇全場景定位位算單元售后 2025-11-06

- 山西高性能位算單元應用 2025-11-06

- 山西智能制造位算單元廠家 2025-11-06

- 山東機器人位算單元定制 2025-11-06

- 四川智能倉儲位算單元定制 2025-11-06

- 浙江全場景定位位算單元二次開發 2025-11-06

- 河北ROS位算單元廠家 2025-11-06

- 北京全場景定位位算單元 2025-11-06

- 無錫機器視覺位算單元廠家 2025-11-06

- 廣東位算單元哪家好 2025-11-06

- 哈爾濱鎧裝熱電偶報價 2025-12-10

- 威海研究無創睡眠監測系統 2025-12-10

- 云南游離氯分析儀表電話 2025-12-10

- 網絡基礎設施監控 2025-12-10

- 杭州灌溉行業電磁流量計 2025-12-10

- 鹽城應用廣恒溫箱商家 2025-12-10

- 合肥品牌船舶自動化監測報警系統市場價 2025-12-10

- 珠海傳感器廠家價格 2025-12-10

- 嘉定區節能溢流閥調整 2025-12-10

- 杭州隔離型差壓變送器 2025-12-10