杭州揚興有源晶振多少錢

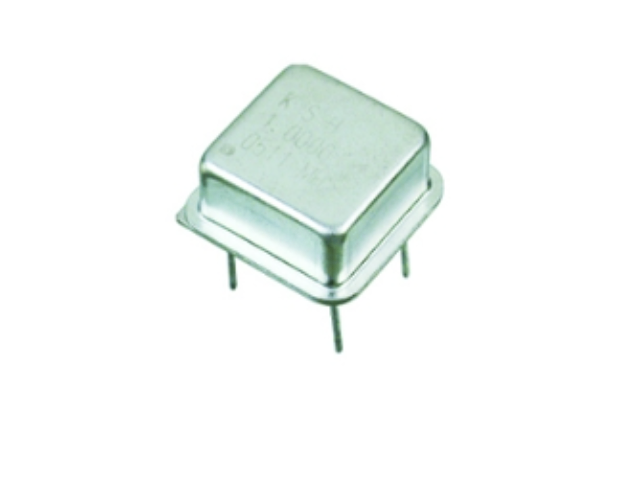

極簡接線邏輯進一步降低組裝復雜度:有源晶振通常只需 2-4 個引腳即可工作(電源正、電源負、信號輸出、使能端,部分簡化型號只需電源與信號端),無需像無源晶振那樣額外連接反饋電阻、負載電容等元件 —— 接線數量減少 60% 以上,組裝時無需逐一核對多根線路的對應關系,降低對組裝人員的技能要求,同時減少因接線錯誤導致的時鐘電路故障(如漏接電容引發的頻率漂移),大幅提升組裝合格率,尤其適合對組裝效率要求高的物聯網傳感器、便攜醫療設備等場景。有源晶振助力設備小型化,減少內部電路占用空間。杭州揚興有源晶振多少錢

在高精度場景中,時鐘信號的噪聲會直接影響系統性能,而有源晶振的低噪聲優勢能有效規避這一問題。從設計來看,有源晶振多采用低噪聲晶體管架構,如差分對管設計,可抑制共模噪聲干擾,同時通過負反饋電路控制信號放大過程,避免放大環節引入額外噪聲,其相位噪聲指標通常能達到 1kHz 偏移時低于 - 130dBc/Hz,遠優于無源晶振搭配外部電路的噪聲表現。對于 5G 通信基站這類高精度場景,信號解調對時鐘相位穩定性要求極高,若時鐘噪聲過大,會導致星座圖偏移,增加誤碼率。有源晶振內置的高精度晶體諧振器,能減少溫度、電壓波動引發的頻率漂移,配合電源濾波單元濾除供電鏈路的紋波噪聲,確保輸出時鐘信號的相位抖動控制在 1ps 以內,保障信號解調精度。肇慶EPSON有源晶振品牌有源晶振輸出信號穩定,減少設備因時鐘問題出現故障。

面對工業現場的強電磁干擾(如變頻器、繼電器產生的雜波),有源晶振內置多級濾波電路與差分輸出接口(如 LVDS):濾波電路可濾除供電鏈路中的紋波噪聲,差分接口能抑制共模干擾,確保時鐘信號相位抖動控制在 1ps 以內,避免干擾導致 PLC 邏輯指令誤觸發,例如生產線傳送帶啟停時序紊亂。此外,工業級有源晶振的長壽命與低失效率設計(MTBF 可達 100 萬小時以上),契合工業設備 “7×24 小時連續運行” 需求,且出廠前經過高溫老化、振動測試等可靠性驗證,無需后期頻繁調試維護,能持續為工業控制設備提供穩定時鐘基準,保障生產流程的連續性與控制精度。

有源晶振能讓設備快速獲取時鐘信號,在于其 “集成化預調試” 設計,徹底省去傳統方案中信號生成的復雜環節,直接為研發提效。從信號獲取邏輯看,有源晶振內置振蕩器、放大電路與穩壓模塊,無需像無源晶振那樣,需研發人員先設計振蕩電路(匹配反相器、反饋電阻)、調試負載電容值(如反復測試 20pF/22pF 電容以校準頻率),只需接入設備的電源(如 1.8V-5V)與信號接口,即可在通電瞬間輸出穩定時鐘信號(如 12MHz/24MHz),信號獲取時間從傳統的 1-2 天縮短至幾分鐘,實現 “即插即用”。智能家居設備需低復雜度設計,有源晶振可助力實現。

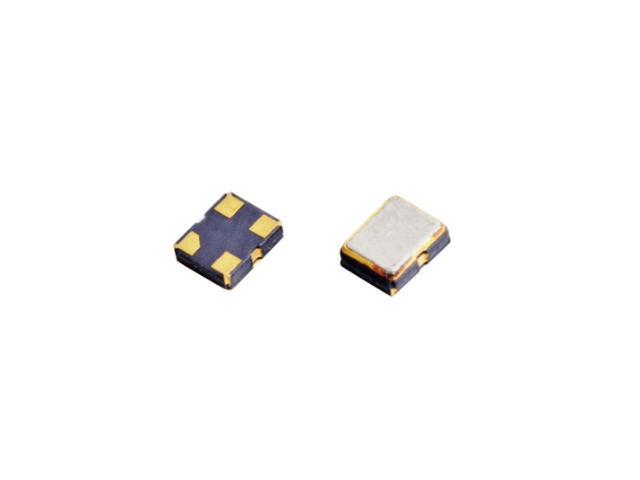

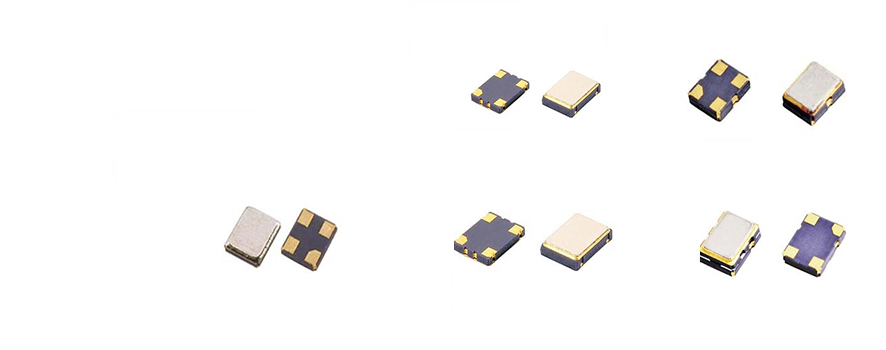

有源晶振能減少外部元件數量,源于其將時鐘信號生成、放大、穩壓等功能集成于單一封裝,直接替代傳統方案中需額外搭配的多類分立元件,從而大幅節省設備內部空間。傳統無源晶振只提供基礎諧振功能,需外部配套 4-6 個元件才能正常工作:包括反相放大器(如 CMOS 反相器芯片)實現信號振蕩、反饋電阻(Rf)與負載電容(Cl1/Cl2)校準振蕩頻率、LDO 穩壓器過濾供電噪聲、π 型濾波網絡(含電感、電容)抑制電源紋波。這些元件需在 PCB 上單獨布局,元件占用的 PCB 面積就達 8-15mm2(以 0402 封裝元件為例)。而有源晶振通過內置振蕩器、低噪聲晶體管放大電路、穩壓單元及濾波電容,只需 1 個封裝(常見尺寸如 3.2mm×2.5mm、2.0mm×1.6mm)即可實現同等功能,直接省去上述外部元件,單時鐘電路模塊的 PCB 空間占用可減少 60% 以上。通信設備對頻率精度要求高,適合搭配有源晶振使用。肇慶EPSON有源晶振品牌

全溫度范圍內,有源晶振頻率穩定度多在 15ppm 至 50ppm 間。杭州揚興有源晶振多少錢

有源晶振的內置驅動設計還能保障信號完整性:其輸出端集成阻抗匹配電阻與信號整形電路,可減少信號傳輸中的反射與串擾,避免外部緩沖電路因阻抗不匹配導致的信號過沖、振鈴等問題。例如工業 PLC 需為 4 個 IO 控制模塊提供時鐘,有源晶振無需外接緩沖即可直接輸出穩定信號,省去緩沖芯片的 PCB 布局空間(約 3mm×2mm)與供電鏈路,同時避免外部緩沖引入的額外噪聲(相位噪聲可能增加 5-10dBc/Hz)。這種設計不僅簡化電路,更確保時鐘信號在多負載場景下的穩定性,適配消費電子、工業控制等多器件協同工作的需求。杭州揚興有源晶振多少錢

- 湖州NDK貼片晶振批發 2025-12-07

- 溫州NDK貼片晶振購買 2025-12-07

- 佛山YXC貼片晶振多少錢 2025-12-07

- 寧波EPSON貼片晶振購買 2025-12-07

- 杭州揚興貼片晶振生產 2025-12-07

- 深圳NDK貼片晶振購買 2025-12-07

- 茂名貼片晶振價格 2025-12-07

- 南京TXC貼片晶振購買 2025-12-07

- 鎮江YXC貼片晶振廠家 2025-12-07

- 舟山NDK貼片晶振現貨 2025-12-07

- 重慶貼片功率電感器 2025-12-07

- 鎮江常見機電組件設備量大從優 2025-12-07

- 虹口區智能GSM模塊量大從優 2025-12-07

- 閔行區本地電力電子元器件銷售客服電話 2025-12-07

- 上海質量無線通信模塊解決方案生產企業 2025-12-07

- 揭陽高速FPC軟板 2025-12-07

- 東莞河道雷達水位傳感器維護方法 2025-12-07

- 廣西靜態傾角儀 2025-12-07

- 合肥40m sff光模塊 2025-12-07

- 荊州醫院led叫號屏供應 2025-12-07