鄭州KDS有源晶振哪里有

在信號放大與穩幅環節,內置晶體管通過負反饋電路實現控制:晶體諧振器初始產生的振蕩信號幅度只為毫伏級,晶體管會對其進行線性放大,同時反饋電路實時監測輸出幅度,若幅度超出標準范圍(如 CMOS 電平的 3.3V±0.2V),則自動調整晶體管的放大倍數,將幅度波動控制在 ±5% 以內,避免信號因幅度不穩導致的時序誤判。此外,內置晶體管還能保障振蕩的持續穩定。傳統無源晶振依賴外部晶體管搭建振蕩電路,若外部元件參數漂移(如溫度導致的放大倍數下降),易出現 “停振” 故障;而有源晶振的晶體管與振蕩電路集成于同一封裝,溫度、電壓變化時,晶體管的電學參數(如電流放大系數 β)與振蕩電路的匹配度始終保持穩定,可在 - 40℃~85℃寬溫范圍內持續維持振蕩,確保輸出信號無中斷、無失真。這種穩定性在工業 PLC、5G 基站等關鍵設備中尤為重要,能直接避免因時鐘信號異常導致的系統停機或數據傳輸錯誤。有源晶振通過內置電路,確保輸出信號的低噪聲特性。鄭州KDS有源晶振哪里有

汽車電子領域對穩定性的要求遠超普通場景,需應對 - 40℃~125℃寬溫(發動機艙可達 150℃)、持續振動(2000Hz 以下)、強電磁干擾(電機 / 高壓線束)及 10 萬小時以上的長壽命需求,有源晶振通過針對性設計可適配這些場景。在寬溫穩定性上,汽車級有源晶振多采用高規格溫補模塊(AEC-Q200 認證的 TCXO),內置高精度熱敏電阻與補償電路,能實時修正晶體因溫變產生的諧振參數偏差。例如在發動機 ECU 中,時鐘信號需控制燃油噴射與點火時序,有源晶振可將 - 40℃~125℃內的頻率穩定度控制在 ±0.5ppm~±2ppm,避免溫漂導致的噴油提前或延遲,防止油耗增加 10% 以上或排放超標,而普通無源晶振在此溫域內穩定度常突破 50ppm,無法滿足需求。西安EPSON有源晶振有源晶振的晶體管保障信號穩定,減少信號波動情況。

低相位抖動是數據傳輸設備的另一需求,高速數據(如 5G 基站的 256QAM 調制信號)對時鐘相位變化極為敏感,相位抖動超 5ps 會導致符號間干擾。有源晶振采用低噪聲晶體管與差分輸出架構,相位抖動可控制在 1ps 以內,避免因時鐘抖動導致的數據幀同步失敗,例如工業以太網設備(如 Profinet)傳輸實時控制數據時,該特性能確保數據幀按毫秒級時序精確收發,無延遲或丟失。此外,數據傳輸設備常處于復雜電磁環境(如基站機房、工業車間),有源晶振內置多級濾波電路與屏蔽封裝,可濾除供電紋波與外部電磁干擾,避免時鐘信號受雜波影響。同時,其支持靈活頻率定制(如 156.25MHz 適配光纖傳輸、250MHz 適配 5G 中頻),無需額外設計分頻電路,可直接匹配不同傳輸速率的時鐘需求,例如千兆以太網設備需 125MHz 時鐘,有源晶振可直接輸出該頻率,省去分頻芯片,簡化設計的同時保障時鐘精確性,為數據傳輸的可靠性提供支撐。

通信設備對頻率的需求集中在 “寬覆蓋、高穩定、低噪聲、可微調” 四大維度,有源晶振的重要參數特性恰好精確匹配,成為通信系統的關鍵時鐘源。從頻率覆蓋范圍看,通信設備需適配多模塊時鐘需求:5G 基站的射頻單元需 2.6GHz 高頻時鐘,光模塊(100Gbps)依賴 156.25MHz 基準時鐘,路由器的主控單元則需 25MHz 低頻時鐘。有源晶振可覆蓋 1kHz-10GHz 頻率范圍,通過不同封裝(如 SMD、DIP)直接適配各模塊,無需額外設計分頻 / 倍頻電路,避免頻率轉換過程中的信號損耗。有源晶振的頻率穩定特性,適配多種高精度電子設備。

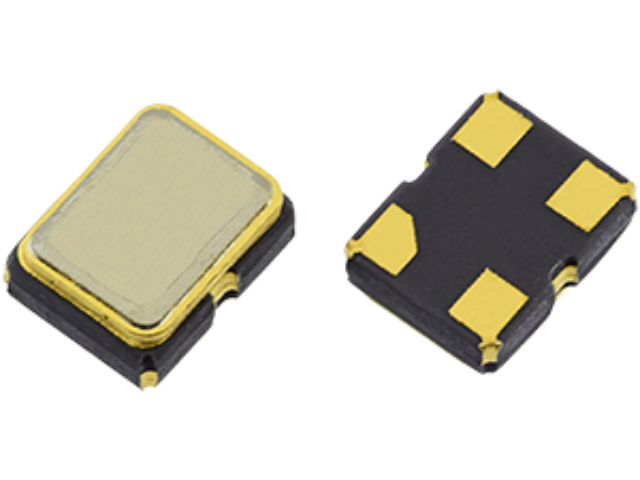

有源晶振的便捷連接特性,從接口、封裝到接線邏輯簡化設備組裝流程,大幅降低操作難度與出錯風險。首先是標準化接口設計,其普遍支持 CMOS、LVDS、ECL 等行業通用輸出接口,可直接與 MCU、FPGA、射頻芯片等器件的時鐘引腳對接 —— 無需像部分特殊時鐘模塊那樣,額外設計接口轉換電路或焊接轉接座,組裝時只需按引腳定義對應焊接,避免因接口不兼容導致的線路修改或元件返工,尤其適合中小批量設備的快速組裝。其次是適配自動化組裝的封裝形式,主流有源晶振采用 SMT(表面貼裝技術)封裝,如 3225(3.2mm×2.5mm)、2520(2.5mm×2.0mm)等規格,引腳布局規整且間距統一(常見 0.5mm/0.8mm 引腳間距),可直接通過貼片機定位焊接,無需手工插裝 —— 相比傳統 DIP(雙列直插)封裝的晶振,省去了穿孔焊接的繁瑣步驟,不僅將單顆晶振的組裝時間從 30 秒縮短至 5 秒,還避免了手工焊接時可能出現的虛焊、錯焊問題,適配消費電子、工業模塊等自動化生產線的組裝需求。有源晶振無需外部振蕩器驅動,簡化設備電路設計流程。成都有源晶振多少錢

有源晶振直接輸出時鐘信號,無需用戶進行額外信號處理。鄭州KDS有源晶振哪里有

有源晶振能讓設備快速獲取時鐘信號,在于其 “集成化預調試” 設計,徹底省去傳統方案中信號生成的復雜環節,直接為研發提效。從信號獲取邏輯看,有源晶振內置振蕩器、放大電路與穩壓模塊,無需像無源晶振那樣,需研發人員先設計振蕩電路(匹配反相器、反饋電阻)、調試負載電容值(如反復測試 20pF/22pF 電容以校準頻率),只需接入設備的電源(如 1.8V-5V)與信號接口,即可在通電瞬間輸出穩定時鐘信號(如 12MHz/24MHz),信號獲取時間從傳統的 1-2 天縮短至幾分鐘,實現 “即插即用”。鄭州KDS有源晶振哪里有

- 惠州NDK貼片晶振采購 2025-12-06

- 南京揚興貼片晶振購買 2025-12-06

- 廣州NDK貼片晶振 2025-12-06

- 鹽城KDS貼片晶振應用 2025-12-06

- 中山KDS貼片晶振生產 2025-12-06

- 深圳KDS貼片晶振 2025-12-06

- 云浮YXC貼片晶振多少錢 2025-12-06

- 江門揚興貼片晶振現貨 2025-12-06

- 湖州EPSON貼片晶振生產 2025-12-06

- 中山EPSON貼片晶振多少錢 2025-12-06

- 蘭州FPC貼片供應商 2025-12-06

- 四川質量板對板連接器價格對比 2025-12-06

- 寧夏船舶壓力分布檢測選型 2025-12-06

- 天津鐵藝鐘機芯批發 2025-12-06

- 福建進口絲包線 2025-12-06

- 中山萬兆網絡濾波器訂做 2025-12-06

- 江蘇新型機電組件設備量大從優 2025-12-06

- 四川22uH大電流色環電感 2025-12-06

- 江蘇定制物聯網控制板加工平臺 2025-12-06

- 貴州鎵電子元器件批發價 2025-12-06