中山EPSON有源晶振價格

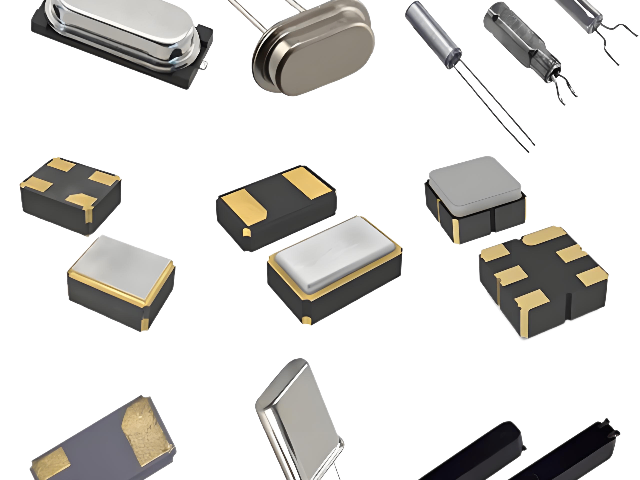

高精度時鐘需求場景(如計量級測試、航空航天、6G 高速通信)對時鐘的**指標要求苛刻 —— 需納級相位抖動、亞 ppm 級頻率穩(wěn)定度及寬溫下的參數一致性,有源晶振憑借底層技術特性,成為這類場景中難以替代的選擇。在測試測量領域,高精度示波器、信號發(fā)生器需時鐘頻率穩(wěn)定度達 ±0.01ppm~±0.1ppm,相位抖動 < 1ps,才能確保電壓、時間測量誤差 < 0.05%。有源晶振的恒溫型號(OCXO)通過恒溫腔將晶體工作溫度波動控制在 ±0.01℃內,頻率穩(wěn)定度可達 ±0.001ppm,相位抖動低至 0.5ps;而無源晶振穩(wěn)定度* ±20ppm~±50ppm,硅振蕩器相位抖動常超 5ps,均無法滿足計量級精度需求,會導致測量數據偏差超 1%,失去校準價值。有源晶振的頻率穩(wěn)定特性,適配多種高精度電子設備。中山EPSON有源晶振價格

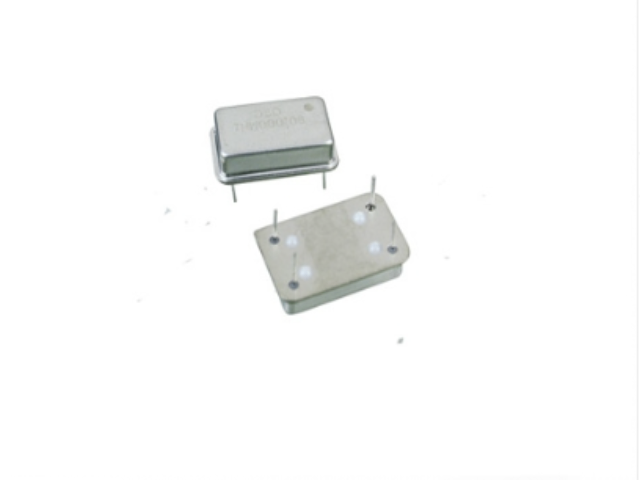

在信號放大與穩(wěn)幅環(huán)節(jié),內置晶體管通過負反饋電路實現控制:晶體諧振器初始產生的振蕩信號幅度只為毫伏級,晶體管會對其進行線性放大,同時反饋電路實時監(jiān)測輸出幅度,若幅度超出標準范圍(如 CMOS 電平的 3.3V±0.2V),則自動調整晶體管的放大倍數,將幅度波動控制在 ±5% 以內,避免信號因幅度不穩(wěn)導致的時序誤判。此外,內置晶體管還能保障振蕩的持續(xù)穩(wěn)定。傳統無源晶振依賴外部晶體管搭建振蕩電路,若外部元件參數漂移(如溫度導致的放大倍數下降),易出現 “停振” 故障;而有源晶振的晶體管與振蕩電路集成于同一封裝,溫度、電壓變化時,晶體管的電學參數(如電流放大系數 β)與振蕩電路的匹配度始終保持穩(wěn)定,可在 - 40℃~85℃寬溫范圍內持續(xù)維持振蕩,確保輸出信號無中斷、無失真。這種穩(wěn)定性在工業(yè) PLC、5G 基站等關鍵設備中尤為重要,能直接避免因時鐘信號異常導致的系統停機或數據傳輸錯誤。蘇州KDS有源晶振生產有源晶振無需外部振蕩器,降低設備的能源消耗。

高低溫環(huán)境下有源晶振能維持 15-50ppm 穩(wěn)定度,依賴針對性的溫度適配設計,從晶體選型、補償機制到封裝防護形成完整保障體系。其采用的高純度石英晶體具有低溫度系數特性,通過切割工藝(如 AT 切型),將晶體本身的溫度頻率漂移控制在 ±30ppm/℃以內,為穩(wěn)定度奠定基礎;更關鍵的是內置溫度補償模塊(TCXO 架構),模塊中的熱敏電阻實時監(jiān)測環(huán)境溫度,將溫度信號轉化為電信號,通過補償電路動態(tài)調整晶體兩端的負載電容或振蕩電路的供電電壓,抵消溫變導致的頻率偏移 —— 例如在 - 40℃低溫時,補償電路會增大負載電容以提升頻率,在 85℃高溫時減小電容以降低頻率,將整體穩(wěn)定度鎖定在 15-50ppm 區(qū)間。

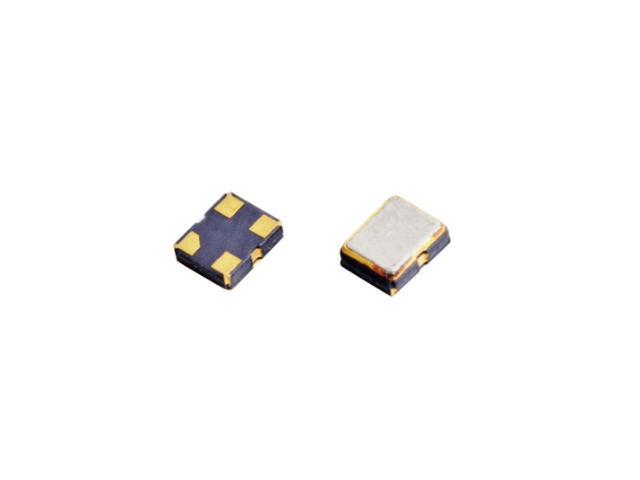

有源晶振通過內置設計完全替代上述調理功能:其一,內置低噪聲放大電路,直接將晶體諧振的毫伏級信號放大至 1.8V-5V 標準電平(支持 CMOS/LVDS/TTL 多電平輸出),無需外接放大器與電平轉換芯片,適配不同芯片的電平需求;其二,集成 LDO 穩(wěn)壓單元與多級 RC 濾波網絡,可將外部供電紋波(如 100mV)抑制至 1mV 以下,濾除 100MHz 以上高頻雜波,替代外部濾波與 EMI 抑制電路;其三,內置阻抗匹配單元(可適配 50Ω/75Ω/100Ω 負載),無需外接匹配電阻,避免信號反射損耗。全溫度范圍內,有源晶振頻率穩(wěn)定度多在 15ppm 至 50ppm 間。

傳統方案中,無源晶振輸出的信號存在多類缺陷,需依賴復雜調理電路彌補:一是信號幅度微弱(只毫伏級),需外接低噪聲放大器(如 OPA847)將信號放大至標準電平(3.3V/5V),否則無法驅動后續(xù)芯片;二是噪聲干擾嚴重,需配置 π 型濾波網絡(含電感、2-3 顆電容)濾除電源紋波,加 EMI 屏蔽濾波器抑制輻射雜波,避免噪聲導致信號失真;三是電平不兼容,若后續(xù)芯片需 LVDS 電平(如 FPGA),而無源晶振輸出 CMOS 電平,需額外加電平轉換芯片(如 SN75LBC184);四是阻抗不匹配,不同負載(如射頻模塊、MCU)需不同阻抗(50Ω/75Ω),需外接匹配電阻(如 0402 封裝的 50Ω 電阻),否則信號反射導致傳輸損耗。這些調理電路需占用 10-15mm2 PCB 空間,且需反復調試參數(如放大器增益、濾波電容容值),增加設計復雜度。有源晶振的高質量輸出,助力設備通過嚴格性能測試。河北KDS有源晶振現貨

有源晶振的穩(wěn)定度參數,符合通信行業(yè)的嚴格標準。中山EPSON有源晶振價格

有源晶振能從電路設計全流程減少工程師的操作步驟,在于其集成化特性替代了傳統方案的多環(huán)節(jié)設計,直接壓縮開發(fā)周期,尤其適配消費電子、物聯網模塊等快迭代領域的需求。在原理圖設計階段,傳統無源晶振需工程師單獨設計振蕩電路(如 CMOS 反相器振蕩架構)、匹配負載電容(12pF-22pF)、反饋電阻(1MΩ-10MΩ),若驅動能力不足還需增加驅動芯片(如 74HC04),只時鐘部分就需繪制 10 余個元件的連接邏輯,步驟繁瑣且易因引腳錯連導致設計失效。而有源晶振內置振蕩、放大、穩(wěn)壓功能,原理圖只需設計 2-3 個引腳(電源正、地、信號輸出)的簡單回路,繪制步驟減少 70% 以上,且無需擔心振蕩電路拓撲錯誤,降低設計返工率。中山EPSON有源晶振價格

- 湖州NDK貼片晶振批發(fā) 2025-12-07

- 溫州NDK貼片晶振購買 2025-12-07

- 佛山YXC貼片晶振多少錢 2025-12-07

- 寧波EPSON貼片晶振購買 2025-12-07

- 杭州揚興貼片晶振生產 2025-12-07

- 深圳NDK貼片晶振購買 2025-12-07

- 茂名貼片晶振價格 2025-12-07

- 南京TXC貼片晶振購買 2025-12-07

- 鎮(zhèn)江YXC貼片晶振廠家 2025-12-07

- 舟山NDK貼片晶振現貨 2025-12-07

- 虹口區(qū)智能GSM模塊量大從優(yōu) 2025-12-07

- 閔行區(qū)本地電力電子元器件銷售客服電話 2025-12-07

- 上海質量無線通信模塊解決方案生產企業(yè) 2025-12-07

- 合肥40m sff光模塊 2025-12-07

- 荊州醫(yī)院led叫號屏供應 2025-12-07

- 禮堂中控矩陣系統廠家 2025-12-07

- 閔行區(qū)質量電子產品銷售銷售價格 2025-12-07

- 蘇州通孔DIP插件量產 2025-12-07

- HTCC電子元器件鍍金廠家 2025-12-07

- CAK37F-25V-50000uF-K-S7 2025-12-07