南昌多芯MT-FA光組件三維芯片傳輸技術(shù)

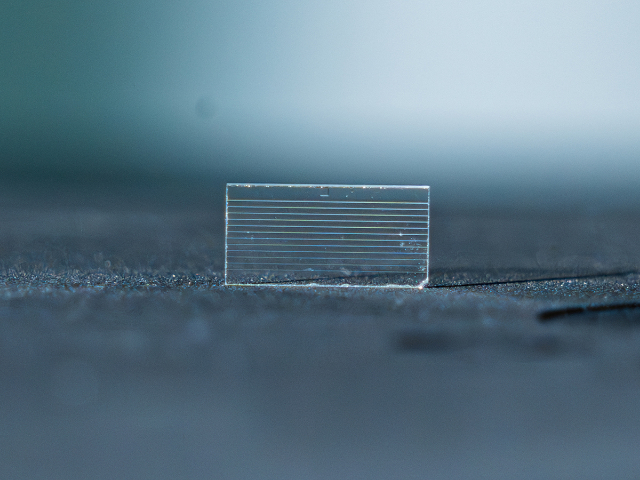

多芯MT-FA光纖連接與三維光子互連的協(xié)同創(chuàng)新,正推動光通信向更高集成度與更低功耗方向演進(jìn)。在800G/1.6T光模塊領(lǐng)域,MT-FA組件通過精密陣列排布技術(shù),將光纖直徑壓縮至125微米量級,同時保持0.3dB以下的插入損耗。這種設(shè)計使得單個光模塊可集成128個并行通道,較傳統(tǒng)方案密度提升4倍。三維光子互連架構(gòu)則進(jìn)一步優(yōu)化了光信號的路由效率:通過波長復(fù)用技術(shù),同一波導(dǎo)可同時傳輸16個不同波長的光信號,每個波長承載50Gbps數(shù)據(jù)流,總帶寬達(dá)800Gbps。在制造工藝層面,光子器件與MT-FA的集成采用28納米CMOS兼容工藝,通過深紫外光刻與反應(yīng)離子蝕刻技術(shù),在硅基底上構(gòu)建出三維光波導(dǎo)網(wǎng)絡(luò)。這種工藝不僅降低了制造成本,更使光子互連層的厚度控制在5微米以內(nèi),與電子芯片的堆疊間隙精確匹配。在物聯(lián)網(wǎng)和邊緣計算領(lǐng)域,三維光子互連芯片的高性能和低功耗特點將發(fā)揮重要作用。南昌多芯MT-FA光組件三維芯片傳輸技術(shù)

在三維光子互連芯片的多芯MT-FA光組件集成實踐中,模塊化設(shè)計與可擴(kuò)展性成為重要技術(shù)方向。通過將光引擎、驅(qū)動芯片和MT-FA組件集成于同一基板,可形成標(biāo)準(zhǔn)化功能單元,支持按需組合以適應(yīng)不同規(guī)模的光互連需求。例如,采用硅基光電子工藝制備的光引擎可與多芯MT-FA直接鍵合,形成從光信號調(diào)制到光纖耦合的全流程集成,減少中間轉(zhuǎn)換環(huán)節(jié)帶來的損耗。針對高密度封裝帶來的散熱挑戰(zhàn),該方案引入微通道液冷或石墨烯導(dǎo)熱層等新型熱管理技術(shù),確保在10W/cm2以上的功率密度下穩(wěn)定運行。測試數(shù)據(jù)顯示,采用三維集成方案的MT-FA組件在85℃高溫環(huán)境中,插損波動小于0.1dB,回波損耗優(yōu)于-30dB,滿足5G前傳、城域網(wǎng)等嚴(yán)苛場景的可靠性要求。未來,隨著光子集成電路(PIC)技術(shù)的進(jìn)一步成熟,多芯MT-FA方案有望向128芯及以上規(guī)模演進(jìn),為全光交換網(wǎng)絡(luò)和量子通信等前沿領(lǐng)域提供底層支撐。高密度多芯MT-FA光組件三維集成供貨報價智能電網(wǎng)建設(shè)中,三維光子互連芯片保障電力系統(tǒng)數(shù)據(jù)的安全高速傳輸。

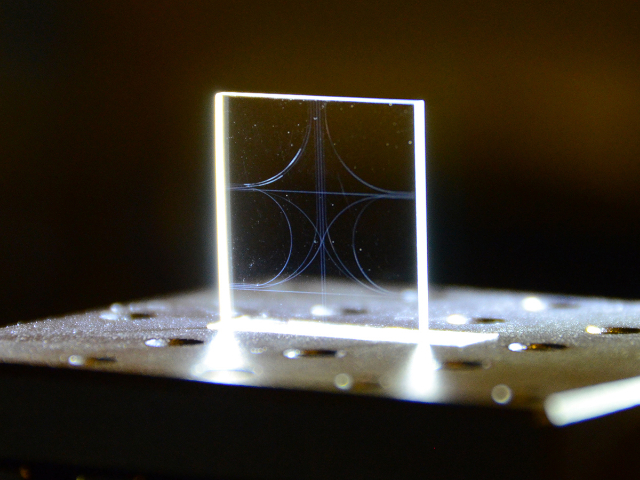

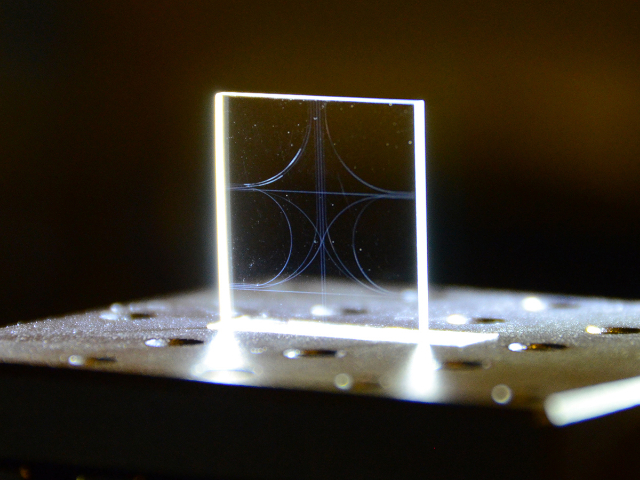

在工藝實現(xiàn)層面,三維光子耦合方案對制造精度提出了嚴(yán)苛要求。光纖陣列的V槽基片需采用納米級光刻與離子束刻蝕技術(shù),確保光纖間距公差控制在±0.5μm以內(nèi),以匹配光芯片波導(dǎo)的排布密度。同時,反射鏡陣列的制備需結(jié)合三維激光直寫與反應(yīng)離子刻蝕,在硅基或鈮酸鋰基底上構(gòu)建曲率半徑小于50μm的微型反射面,并通過原子層沉積技術(shù)鍍制高反射率金屬膜層,使反射效率達(dá)99.5%以上。耦合過程中,需利用六軸位移臺與高精度視覺定位系統(tǒng),實現(xiàn)光纖陣列與反射鏡陣列的亞微米級對準(zhǔn),并通過環(huán)氧樹脂低溫固化工藝確保長期穩(wěn)定性。測試數(shù)據(jù)顯示,采用該方案的光模塊在40℃高溫環(huán)境下連續(xù)運行2000小時后,插入損耗波動低于0.1dB,回波損耗穩(wěn)定在60dB以上,充分驗證了三維耦合方案在嚴(yán)苛環(huán)境下的可靠性。隨著空分復(fù)用(SDM)技術(shù)的成熟,三維光子耦合方案將成為構(gòu)建T比特級光互聯(lián)系統(tǒng)的重要基礎(chǔ)。

高性能多芯MT-FA光組件的三維集成方案通過突破傳統(tǒng)二維平面布局的物理限制,實現(xiàn)了光信號傳輸密度與系統(tǒng)可靠性的雙重提升。該方案以多芯光纖陣列(Multi-FiberTerminationFiberArray)為重要載體,通過精密研磨工藝將光纖端面加工成特定角度,結(jié)合低損耗MT插芯實現(xiàn)端面全反射,使多路光信號在毫米級空間內(nèi)完成并行傳輸。與傳統(tǒng)二維布局相比,三維集成技術(shù)通過層間耦合器將不同波導(dǎo)層的光信號進(jìn)行垂直互聯(lián),例如采用倏逝波耦合器或3D波導(dǎo)耦合器實現(xiàn)層間光場的高效轉(zhuǎn)換,明顯提升了單位面積內(nèi)的通道數(shù)量。實驗數(shù)據(jù)顯示,采用三維堆疊技術(shù)的MT-FA組件可在800G光模塊中實現(xiàn)12通道并行傳輸,通道間距壓縮至0.25mm,較傳統(tǒng)方案提升40%的集成度。同時,通過飛秒激光直寫技術(shù)對玻璃基板進(jìn)行三維微納加工,可精確控制V槽(V-Groove)的深度與角度公差,確保多芯光纖的定位精度優(yōu)于±0.5μm,從而降低插入損耗至0.2dB以下,滿足AI算力集群對長距離、高負(fù)荷數(shù)據(jù)傳輸?shù)姆€(wěn)定性要求。三維光子互連芯片的垂直互連技術(shù),不僅提升了數(shù)據(jù)傳輸效率,還優(yōu)化了芯片內(nèi)部的布局結(jié)構(gòu)。

該標(biāo)準(zhǔn)的演進(jìn)正推動光組件與芯片異質(zhì)集成技術(shù)的深度融合。在制造工藝維度,三維互連標(biāo)準(zhǔn)明確要求MT-FA組件需兼容2.5D/3D封裝流程,包括晶圓級薄化、臨時鍵合解鍵合、熱壓鍵合等關(guān)鍵步驟。其中,晶圓薄化后的翹曲度需控制在5μm以內(nèi),以確保與TSV中介層的精確對準(zhǔn)。對于TGV技術(shù),標(biāo)準(zhǔn)規(guī)定激光誘導(dǎo)濕法刻蝕的側(cè)壁垂直度需優(yōu)于85°,深寬比突破6:1限制,使玻璃基三維集成的信號完整性達(dá)到硅基方案的90%以上。在系統(tǒng)級應(yīng)用層面,標(biāo)準(zhǔn)定義了多芯MT-FA與CPO(共封裝光學(xué))架構(gòu)的接口規(guī)范,要求光引擎與ASIC芯片的垂直互連延遲低于2ps/mm,功耗密度不超過15pJ/bit。這種技術(shù)整合使得單模塊可支持1.6Tbps傳輸速率,同時將系統(tǒng)級功耗降低40%。值得關(guān)注的是,標(biāo)準(zhǔn)還納入了可靠性測試條款,包括-40℃至125℃溫度循環(huán)下的1000次熱沖擊測試、85%RH濕度環(huán)境下的1000小時穩(wěn)態(tài)試驗,確保三維互連結(jié)構(gòu)在數(shù)據(jù)中心長期運行中的穩(wěn)定性。隨著AI大模型參數(shù)規(guī)模突破萬億級,此類標(biāo)準(zhǔn)的完善正為光通信與集成電路的協(xié)同創(chuàng)新提供關(guān)鍵技術(shù)底座。三維光子互連芯片的出現(xiàn),為數(shù)據(jù)中心的高效能管理提供了全新解決方案。高密度多芯MT-FA光組件三維集成供貨報價

Lightmatter的L200X芯片,通過3D集成實現(xiàn)64Tbps共封裝光學(xué)帶寬。南昌多芯MT-FA光組件三維芯片傳輸技術(shù)

三維光子集成多芯MT-FA光接口方案是應(yīng)對AI算力爆發(fā)式增長與數(shù)據(jù)中心超高速互聯(lián)需求的重要技術(shù)突破。該方案通過將三維光子集成技術(shù)與多芯MT-FA(多纖終端光纖陣列)深度融合,實現(xiàn)了光子層與電子層在垂直維度的深度耦合。傳統(tǒng)二維光子集成受限于芯片面積,難以同時集成高密度光波導(dǎo)與大規(guī)模電子電路,而三維集成通過TSV(硅通孔)與銅柱凸點鍵合技術(shù),將光子芯片與CMOS電子芯片垂直堆疊,形成80通道以上的超密集光子-電子混合系統(tǒng)。以某研究機構(gòu)展示的80通道三維集成芯片為例,其采用15μm間距的銅柱凸點陣列,通過2304個鍵合點實現(xiàn)光子層與電子層的低損耗互連,發(fā)射器與接收器單元分別集成20個波導(dǎo)總線,每個總線支持4個波長通道,實現(xiàn)了單芯片1.6Tbps的傳輸容量。這種設(shè)計突破了傳統(tǒng)光模塊中光子與電子分離布局的帶寬瓶頸,使電光轉(zhuǎn)換能耗降至120fJ/bit,較早期二維方案降低50%以上。南昌多芯MT-FA光組件三維芯片傳輸技術(shù)

- 北京多芯MT-FA扇入扇出代工 2025-12-06

- 無錫多芯MT-FA光組件技術(shù)參數(shù) 2025-12-06

- 溫州多芯MT-FA光組件 2025-12-06

- 多芯MT-FA光纖陣列扇入器多少錢 2025-12-05

- 上海多芯MT-FA光通信組件 2025-12-05

- 甘肅多芯MT-FA光組件在城域網(wǎng)中的應(yīng)用 2025-12-05

- 廣西多芯MT-FA光纖陣列扇入器 2025-12-05

- 北京多芯MT-FA光組件行業(yè)解決方案 2025-12-05

- 重慶MT-FA多芯光組件耐溫性能 2025-12-04

- 長沙多芯MT-FA光組件在AI算力中的應(yīng)用 2025-12-04

- 閔行區(qū)附近數(shù)據(jù)集成服務(wù)供應(yīng) 2025-12-06

- 蘇州質(zhì)量光通信設(shè)備廠家報價 2025-12-06

- LIMSlims流程管理主要功能特點 2025-12-06

- 奉賢區(qū)附近工業(yè)設(shè)計服務(wù)推薦貨源 2025-12-06

- 南通電話光纖通信設(shè)備質(zhì)量 2025-12-06

- 錫山區(qū)本地?zé)o線通信系統(tǒng) 2025-12-06

- 南京ESP32開發(fā)Wi-Fi6E低功耗 2025-12-06

- 江蘇智能化光通信設(shè)備廠家報價 2025-12-06

- 循環(huán)發(fā)卡酒店自助機 2025-12-06

- 無線衛(wèi)星定位防盜 2025-12-06