半導(dǎo)體封裝測(cè)試廠

為應(yīng)對(duì)Chiplet集成挑戰(zhàn),中清航科推出自主知識(shí)產(chǎn)權(quán)的混合鍵合(HybridBonding)平臺(tái)。采用銅-銅直接鍵合工藝,凸點(diǎn)間距降至5μm,互連密度達(dá)10?/mm2。其測(cè)試芯片在16核處理器集成中實(shí)現(xiàn)8Tbps/mm帶寬,功耗只為傳統(tǒng)方案的1/3。中清航科研發(fā)的納米銀燒結(jié)膠材料突破高溫封裝瓶頸。在SiC功率模塊封裝中,燒結(jié)層導(dǎo)熱系數(shù)達(dá)250W/mK,耐受溫度600℃,使模塊壽命延長(zhǎng)5倍。該材料已通過ISO26262認(rèn)證,成為新能源汽車OBC充電模組優(yōu)先選擇方案。車規(guī)芯片封裝求穩(wěn),中清航科全生命周期測(cè)試,確保十年以上可靠運(yùn)行。半導(dǎo)體封裝測(cè)試廠

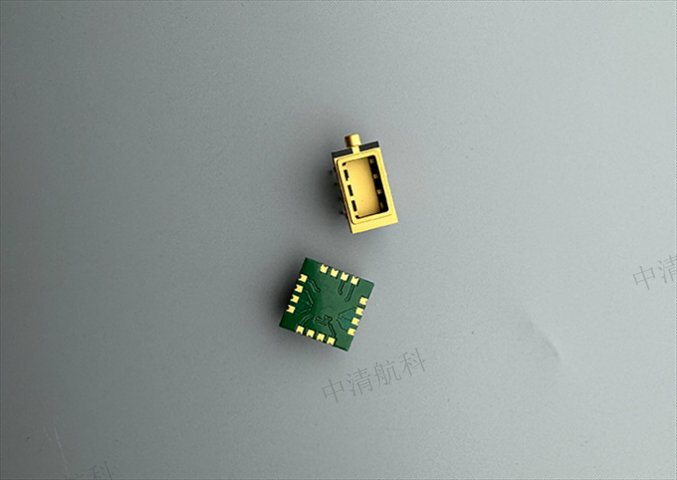

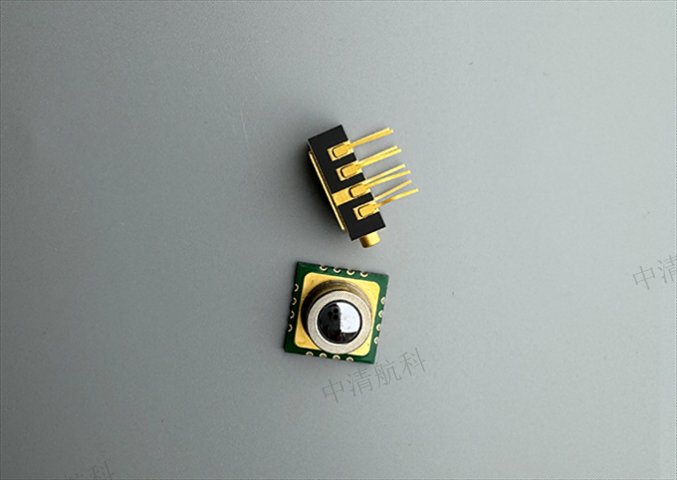

針對(duì)TMR傳感器靈敏度,中清航科開發(fā)磁屏蔽封裝。坡莫合金屏蔽罩使外部場(chǎng)干擾<0.1mT,分辨率達(dá)50nT。電流傳感器精度達(dá)±0.5%,用于新能源汽車BMS系統(tǒng)。中清航科微型熱電發(fā)生器實(shí)現(xiàn)15%轉(zhuǎn)換效率。Bi?Te?薄膜與銅柱互聯(lián)結(jié)構(gòu)使輸出功率密度達(dá)3mW/cm2(ΔT=50℃)。物聯(lián)網(wǎng)設(shè)備實(shí)現(xiàn)供能。中清航科FeRAM封裝解決數(shù)據(jù)保持難題。鋯鈦酸鉛薄膜與耐高溫電極使1012次讀寫后數(shù)據(jù)保持率>99%。125℃環(huán)境下數(shù)據(jù)保存超10年,適用于工業(yè)控制存儲(chǔ)。上海圓晶體封裝公司中清航科芯片封裝技術(shù),平衡電氣性能與機(jī)械保護(hù),延長(zhǎng)芯片使用壽命。

先進(jìn)芯片封裝技術(shù)-系統(tǒng)級(jí)封裝(SiP):SiP是將多個(gè)不同功能的芯片以并排或疊加的方式,封裝在一個(gè)單一的封裝體內(nèi),實(shí)現(xiàn)系統(tǒng)級(jí)的功能集成。與SoC(系統(tǒng)級(jí)芯片)相比,SiP無(wú)需復(fù)雜的IP授權(quán),設(shè)計(jì)更靈活、成本更低。中清航科在SiP技術(shù)上積累了豐富經(jīng)驗(yàn),能夠根據(jù)客戶需求,將多種芯片高效整合在一個(gè)封裝內(nèi),為客戶提供具有成本優(yōu)勢(shì)的系統(tǒng)級(jí)封裝解決方案,廣泛應(yīng)用于消費(fèi)電子、汽車電子等領(lǐng)域。想要了解更多詳細(xì)內(nèi)容可以關(guān)注我司官網(wǎng)。

中清航科部署封裝數(shù)字孿生系統(tǒng),通過AI視覺檢測(cè)實(shí)現(xiàn)微米級(jí)缺陷捕捉。在BGA植球工藝中,球徑一致性控制±3μm,位置精度±5μm。智能校準(zhǔn)系統(tǒng)使設(shè)備換線時(shí)間縮短至15分鐘,產(chǎn)能利用率提升至90%。針對(duì)HBM內(nèi)存堆疊需求,中清航科開發(fā)超薄芯片處理工藝。通過臨時(shí)鍵合/解鍵合技術(shù)實(shí)現(xiàn)50μm超薄DRAM晶圓加工,4層堆疊厚度400μm。其TSV深寬比達(dá)10:1,阻抗控制在30mΩ以下,滿足GDDR6X1TB/s帶寬要求。中清航科可拉伸封裝技術(shù)攻克可穿戴設(shè)備難題。采用蛇形銅導(dǎo)線與彈性體基底結(jié)合,使LED陣列在100%拉伸形變下保持導(dǎo)電功能。醫(yī)療級(jí)生物相容材料通過ISO10993認(rèn)證,已用于動(dòng)態(tài)心電圖貼片量產(chǎn)。中清航科芯片封裝技術(shù),通過電磁兼容設(shè)計(jì),降低多芯片間信號(hào)干擾。

隨著摩爾定律逼近物理極限,先進(jìn)封裝成為提升芯片性能的關(guān)鍵路徑。中清航科在Fan-Out晶圓級(jí)封裝(FOWLP)領(lǐng)域?qū)崿F(xiàn)突破,通過重構(gòu)晶圓級(jí)互連架構(gòu),使I/O密度提升40%,助力5G射頻模塊厚度縮減至0.3mm。其開發(fā)的激光解鍵合技術(shù)將良率穩(wěn)定在99.2%以上,為毫米波通信設(shè)備提供可靠封裝方案。面對(duì)異構(gòu)集成需求激增,中清航科推出3DSiP立體封裝平臺(tái)。該方案采用TSV硅通孔技術(shù)與微凸點(diǎn)鍵合工藝,實(shí)現(xiàn)CPU、HBM內(nèi)存及AI加速器的垂直堆疊。在數(shù)據(jù)中心GPU領(lǐng)域,其散熱增強(qiáng)型封裝結(jié)構(gòu)使熱阻降低35%,功率密度提升至8W/mm2,滿足超算芯片的嚴(yán)苛要求。中清航科深耕芯片封裝,以技術(shù)創(chuàng)新為引擎,助力中國(guó)芯片產(chǎn)業(yè)突破升級(jí)。浙江TO封裝芯片

中清航科芯片封裝方案,通過模塊化接口,簡(jiǎn)化下游廠商應(yīng)用難度。半導(dǎo)體封裝測(cè)試廠

先進(jìn)芯片封裝技術(shù)-晶圓級(jí)封裝(WLP):晶圓級(jí)封裝是在晶圓上進(jìn)行封裝工藝,實(shí)現(xiàn)了芯片尺寸與封裝尺寸的接近,減小了封裝體積,提高了封裝密度。與傳統(tǒng)先切割晶圓再封裝不同,它是先封裝后切割晶圓。中清航科的晶圓級(jí)封裝技術(shù)處于行業(yè)前沿,能夠?yàn)榭蛻籼峁└呒啥取⑿⌒突男酒庋b產(chǎn)品,在物聯(lián)網(wǎng)、可穿戴設(shè)備等對(duì)芯片尺寸和功耗要求苛刻的領(lǐng)域具有廣闊應(yīng)用前景。想要了解更多內(nèi)容可以關(guān)注我司官網(wǎng),另外有相關(guān)需求歡迎隨時(shí)聯(lián)系。半導(dǎo)體封裝測(cè)試廠

- 上海sip多芯片封裝 2025-12-06

- 上海陶瓷封裝企業(yè) 2025-12-06

- 嘉興流片代理一般多少錢 2025-12-06

- 鹽城流片代理推薦廠家 2025-12-06

- 浙江金屬氣密封裝 2025-12-06

- 上海半導(dǎo)體陶瓷封裝 2025-12-06

- 中芯國(guó)際 180流片代理市場(chǎng)價(jià) 2025-12-06

- 上海半導(dǎo)體封裝基板 2025-12-06

- 江蘇光學(xué)傳感器封裝 2025-12-06

- 浙江芯片晶圓切割刀片 2025-12-06

- 深圳臥式NAS機(jī)箱 2025-12-06

- 浙江穩(wěn)定性共享云桌面解決方案 2025-12-06

- 鹽城分離萃取設(shè)備哪幾種 2025-12-06

- 上海sip多芯片封裝 2025-12-06

- 北京打印紙產(chǎn)品介紹 2025-12-06

- 初中物理模擬實(shí)驗(yàn)室系統(tǒng)推薦 2025-12-06

- 四川省智能物流貨代系統(tǒng)推薦 2025-12-06

- 西安線上獲客的定位 2025-12-06

- 連云港通用智慧醫(yī)療參考價(jià) 2025-12-06

- 福建工廠數(shù)字能源產(chǎn)品價(jià)格 2025-12-06