浙江dip8封裝外殼

中清航科超細間距倒裝焊工藝突破10μm極限。采用激光輔助自對準技術,使30μm微凸點對位精度達±1μm。在CIS圖像傳感器封裝中,該技術消除微透鏡偏移問題,提升低光照下15%成像質量。中清航科開發出超薄中心less基板,厚度100μm。通過半加成法(mSAP)實現2μm線寬/間距,傳輸損耗低于0.3dB/mm@56GHz。其5G毫米波AiP天線封裝方案已通過CTIAOTA認證,輻射效率達72%。為響應歐盟RoHS2.0標準,中清航科推出無鉛高可靠性封裝方案。采用Sn-Bi-Ag合金凸點,熔點138℃且抗跌落性能提升3倍。其綠色電鍍工藝使廢水重金屬含量降低99%,獲三星Eco-Partner認證。中清航科專注芯片封裝,通過材料革新讓微型化與高效能兼得。浙江dip8封裝外殼

針對5nm芯片200W+熱功耗挑戰,中清航科開發嵌入式微流道冷卻封裝。在2.5D封裝中介層內蝕刻50μm微通道,采用兩相冷卻液實現芯片級液冷。實測顯示熱點溫度降低48℃,同時節省80%外部散熱空間,為AI服務器提供顛覆性散熱方案。基于低溫共燒陶瓷(LTCC)技術,中清航科推出毫米波天線集成封裝。將24GHz雷達天線陣列直接封裝于芯片表面,信號傳輸距離縮短至0.2mm,插損低于0.5dB。該方案使77GHz車規雷達模塊尺寸縮小60%,量產良率突破95%行業瓶頸。上海封裝殼體中清航科芯片封裝方案,適配車規級嚴苛要求,助力汽車電子安全升級。

面對量子比特超導封裝難題,中清航科開發藍寶石基板微波諧振腔技術。通過超導鋁薄膜微加工,實現5GHz諧振頻率下Q值>100萬,比特相干時間提升至200μs。該方案已用于12量子比特模塊封裝,退相干率降低40%,為量子計算機提供穩定基礎。針對AI邊緣計算需求,中清航科推出近存計算3D封裝。將RRAM存算芯片與邏輯單元垂直集成,互連延遲降至0.1ps/mm。實測顯示ResNet18推理能效達35TOPS/W,較傳統方案提升8倍,滿足端側設備10mW功耗要求。

針對車規級芯片AEC-Q100認證痛點,中清航科建成零缺陷封裝產線。通過銅柱凸點替代錫球焊接,結合環氧模塑料(EMC)三重防護層,使QFN封裝產品在-40℃~150℃溫度循環中通過3000次測試。目前已有17家Tier1供應商采用其AEC-QGrade1封裝解決方案。中清航科多芯片重構晶圓(ReconstitutedWafer)技術,將不同尺寸芯片集成于300mm載板。通過動態貼裝算法優化芯片排布,材料利用率提升至92%,較傳統WLCSP降低成本28%。該方案已應用于物聯網傳感器批量生產,單月產能達500萬顆。超算芯片多芯片協同,中清航科先進封裝,降低芯片間數據傳輸延遲。

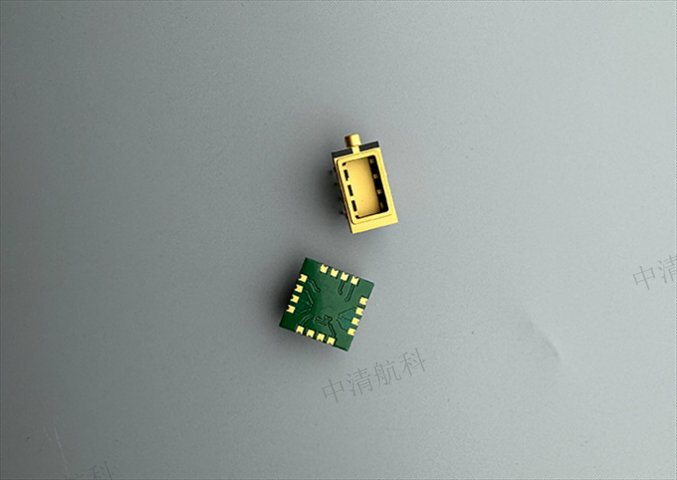

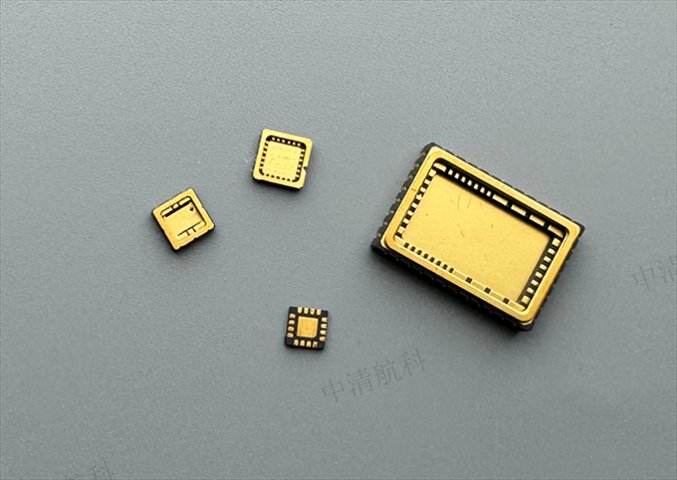

芯片封裝的發展歷程:自20世紀80年代起,芯片封裝技術歷經多代變革。從早期的引腳插入式封裝,如DIP(雙列直插式封裝),發展到表面貼片封裝,像QFP(塑料方形扁平封裝)、PGA(針柵陣列封裝)等。而后,BGA(球柵陣列封裝)、MCP(多芯片模塊)、SIP(系統級封裝)等先進封裝形式不斷涌現。中清航科緊跟芯片封裝技術發展潮流,不斷升級自身技術工藝,在各個發展階段都積累了豐富經驗,能為客戶提供符合不同時期技術標準和市場需求的封裝服務。中清航科芯片封裝技術,支持三維堆疊,突破平面集成的性能天花板。qfn32封裝

中清航科芯片封裝方案,適配邊緣計算設備,平衡性能與功耗需求。浙江dip8封裝外殼

中清航科MIL-STD-883認證產線實現金錫共晶焊接工藝。在宇航級FPGA封裝中,氣密封裝漏率<5×10??atm·cc/s,耐輻照總劑量達100krad。三防涂層通過96小時鹽霧試驗,服務12個衛星型號項目。中清航科推出玻璃基板中介層技術,介電常數低至5.2@10GHz。通過TGV玻璃通孔實現光子芯片與電芯片混合集成,耦合損耗<1dB。該平臺已用于CPO共封裝光學引擎開發,傳輸功耗降低45%。中清航科建立全維度失效分析實驗室。通過3DX-Ray實時監測BGA焊點裂紋,結合聲掃顯微鏡定位分層缺陷。其加速壽命測試模型可精確預測封裝產品在高溫高濕(85℃/85%RH)條件下的10年失效率。浙江dip8封裝外殼

- 上海sip多芯片封裝 2025-12-06

- 江蘇藍寶石晶圓切割企業 2025-12-06

- 紹興sic晶圓切割寬度 2025-12-06

- 江蘇dil封裝管殼 2025-12-06

- 上海陶瓷封裝企業 2025-12-06

- 嘉興流片代理一般多少錢 2025-12-06

- 鹽城流片代理推薦廠家 2025-12-06

- 浙江金屬氣密封裝 2025-12-06

- 上海半導體陶瓷封裝 2025-12-06

- 中芯國際 180流片代理市場價 2025-12-06

- 激光一體機辦公設備租賃耗材全包 2025-12-06

- 佛山服裝吊牌打印機直銷 2025-12-06

- 天津國家無線電SRRC認證哪家便宜 2025-12-06

- 惠州星級賓館管理系統哪家專業 2025-12-06

- 虹口區定制科學計算軟件比較 2025-12-06

- 徐匯區智能AUTOSAR工具鏈24小時服務 2025-12-06

- 深圳臥式NAS機箱 2025-12-06

- 浙江穩定性共享云桌面解決方案 2025-12-06

- 鹽城分離萃取設備哪幾種 2025-12-06

- 個性化校企合作管理模式 2025-12-06